# مكتبة عالم الإلكترون 4electron.com

إلى قارئ هذا الكتاب ، تحية طيبة وبعد ...

لقد أصبحنا نعيش في عالم يعج بالأبحاث والكتب والمعلومات، وأصبح العلم معياراً حقيقياً لتفاضل الأمم والدول والمؤسسات والأشخاص على حدِّ سواء، وقد أمسى بدوره حلاً شبه وحيدٍ لأكثر مشاكل العالم حدة وخطورة، فالبيئة تبحث عن حلول، وصحة الإنسان تبحث عن حلول، والموارد التي تشكل حاجة أساسية للإنسان تبحث عن حلول كذلك، والطاقة والغذاء والماء جميعها تحديات يقف العلم في وجهها الآن ويحاول أن يجد الحلول لها. فأين نحن من هذا العلم ؟ وأين هو منا؟

نسعى في موقع عالم الإلكترون <u>www.4electron.com</u> لأن نوفر بين أيدي كل من حمل على عاتقه مسيرة درب تملؤه التحديات ما نستطيع من أدوات تساعده في هذا الدرب، من مواضيع علمية، ومراجع أجنبية بأحدث إصداراتها، وساحات لتبادل الآراء والأفكار العلمية والمرتبطة بحياتنا الهندسية، وشروح لأهم برمجيات الحاسب التي تتداخل مع تطبيقات الحياة الأكاديمية والعملية، ولكننا نتوقع في نفس الوقت أن نجد بين الطلاب والمهندسين والباحثين من يسعى مثلنا لتحقيق النفع والفائدة للجميع، ويحلم أن يكون عضواً في مجتمع يساهم بتحقيق بيئة خصبة للمواهب والإبداعات والتألق، فهل تحلم بذلك ؟

حاول أن تساهم بفكرة، بومضة من خواطر تفكيرك العلمي، بفائدة رأيتها في إحدى المواضيع العلمية، بجانب مضيء لمحته خلف ثنايا مفهوم هندسي ما. تأكد بأنك ستلتمس الفائدة في كل خطوة تخطوها، وترى غيرك يخطوها معك ...

أخي القارئ، نرجو أن يكون هذا الكتاب مقدمة لمشاركتك في عالمنا العلمي التعاوني، وسيكون موقعكم عالم الإلكترون ww.4electron.com بكل الإمكانيات المتوفرة لديه جاهزاً على الدوام لأن يحقق البيئة والواقع الذي يبحث عنه كل باحث أو طالب في علوم الهندسة، ويسعى فيه للإفادة كل ساع، فأهلاً وسهلاً بكم.

مع تحيات إدارة الموقع وفريق عمله

4

www.4electron.com

موقع عالم الإلكترون www.4electron.com

# Newnes Interfacing Companion

To Robert Winston Cheary, friend and teacher.

# Newnes Interfacing Companion

# A.C. Fischer-Cripps

OXFORD AMSTERDAM BOSTON LONDON NEW YORK PARIS SAN DIEGO SAN FRANCISCO SINGAPORE SYDNEY TOKYO

Newnes An imprint of Elsevier Science Linacre House, Jordan Hill, Oxford OX2 8DP 225 Wildwood Avenue, Woburn MA 01801-2041

First published 2002

Copyright © 2002, A. C. Fischer-Cripps. All rights reserved

The right of A. C. Fischer-Cripps to be identified as the author of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988

No part of this publication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1T 4LP. Applications for the copyright holder's written permission to reproduce any part of this publication should be addressed to the publisher

# **British Library Cataloguing in Publication Data**

A catalogue record for this book is available from the British Library

#### **Library of Congress Cataloguing in Publication Data**

A catalogue record for this book is available from the Library of Congress

ISBN 0750657200

For information on all Newnes publications visit our website at www.newnespress.com

Printed and bound in Great Britain

| Preface                                  | ix |

|------------------------------------------|----|

| Part 1: Transducers                      | 1  |

| 1.0 Transducers                          | 2  |

| 1.1 Measurement systems                  | 3  |

| 1.1.1 Transducers                        | 4  |

| 1.1.2 Methods of measurement             | 5  |

| 1.1.3 Sensitivity                        | 6  |

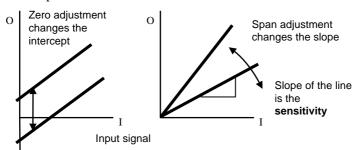

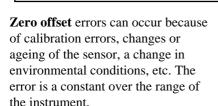

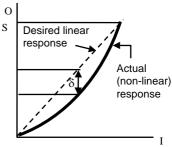

| 1.1.4 Zero, linearity and span           | 7  |

| 1.1.5 Resolution, hysteresis and error   | 8  |

| 1.1.6 Fourier analysis                   | 9  |

| 1.1.7 Dynamic response                   | 10 |

| 1.1.8 PID control                        | 11 |

| 1.1.9 Accuracy and repeatability         | 12 |

| 1.1.10 Mechanical models                 | 13 |

| 1.1.11 Review questions                  | 14 |

| 1.2 Temperature                          | 15 |

| 1.2.1 Temperature                        | 16 |

| 1.2.2 Standard thermometers              | 17 |

| 1.2.3 Industrial thermometers            | 18 |

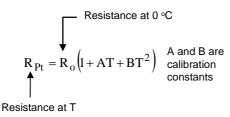

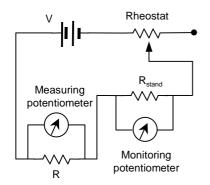

| 1.2.4 Platinum resistance thermometer    | 19 |

| 1.2.5 Liquid-in-glass thermometer        | 20 |

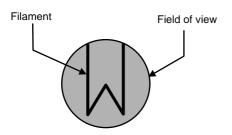

| 1.2.6 Radiation pyrometer                | 21 |

| 1.2.7 Thermocouple                       | 22 |

| 1.2.8 Thermistors                        | 24 |

| 1.2.9 Relative humidity                  | 25 |

| 1.2.10 Review questions                  | 26 |

| 1.2.11 Activities                        | 28 |

| 1.3 Light                                | 34 |

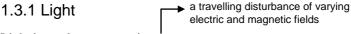

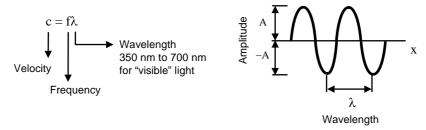

| 1.3.1 Light                              | 35 |

| 1.3.2 Measuring light                    | 36 |

| 1.3.3 Standards of measurement           | 37 |

| 1.3.4 Thermal detectors                  | 38 |

| 1.3.5 Light dependent resistor (LDR)     | 39 |

| 1.3.6 Photodiode                         | 40 |

| 1.3.7 Other semiconductor photodetectors | 41 |

| 1.3.8 Optical detectors                  | 42 |

| 1.3.9 Photomultiplier                    | 43 |

| 1.3.10 Review questions                  | 44 |

| 1.4 Position and motion                  | 45 |

| 1.4.1 Mechanical switch                  | 46 |

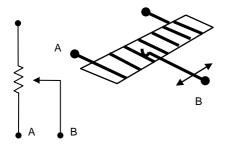

| 1.4.2 Potentiometric sensor              | 47 |

| 1.4.3 Capacitive transducer              | 48 |

| 1.4.4 LVDT                                 | 49 |

|--------------------------------------------|----|

| 1.4.5 Angular velocity transducer          | 50 |

| 1.4.6 Position sensitive diode array       | 51 |

| 1.4.7 Motion control                       | 52 |

| 1.4.9 Review questions                     | 53 |

| 1.5 Force, pressure and flow               | 54 |

| 1.5.1 Strain gauge                         | 55 |

| 1.5.2 Force                                | 57 |

| 1.5.3 Piezoelectric sensor instrumentation | 58 |

| 1.5.4 Acceleration and vibration           | 59 |

| 1.5.5 Mass                                 | 60 |

| 1.5.6 Atmospheric pressure                 | 61 |

| 1.5.7 Pressure                             | 63 |

| 1.5.8 Industrial pressure measurement      | 64 |

| 1.5.9 Sound                                | 65 |

| 1.5.10 Flow                                | 66 |

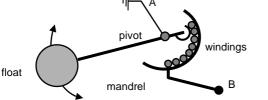

| 1.5.11 Level                               | 69 |

| 1.5.12 Review questions                    | 70 |

|                                            |    |

| Part 2: Interfacing                        | 71 |

| 2.0 Interfacing                            | 72 |

| 2.1 Number systems                         | 73 |

| 2.1.1 Binary number system                 | 74 |

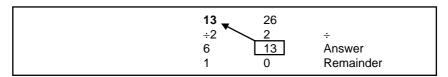

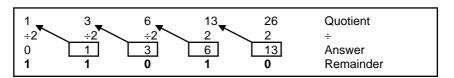

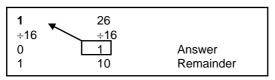

| 2.1.2 Decimal to binary conversion         | 75 |

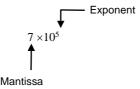

| 2.1.3 Hexadecimal                          | 76 |

| 2.1.4 Decimal to hex conversion            | 77 |

| 2.1.5 2 s complement                       | 78 |

| 2.1.6 Signed numbers                       | 79 |

| 2.1.7 Subtraction and multiplication       | 80 |

| 2.1.8 Binary coded decimal (BCD)           | 81 |

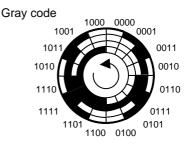

| 2.1.9 Gray code                            | 82 |

| 2.1.10 ASCII code                          | 83 |

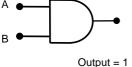

| 2.1.11 Boolean algebra                     | 84 |

| 2.1.12 Digital logic circuits              | 85 |

| 2.1.13 Review questions                    | 86 |

| 2.1.14 Activities                          | 87 |

| 2.2 Computer architecture                  | 88 |

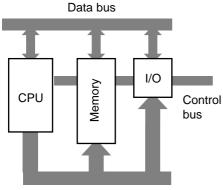

| 2.2.1 Computer architecture                | 89 |

| 2.2.2 Memory                               | 90 |

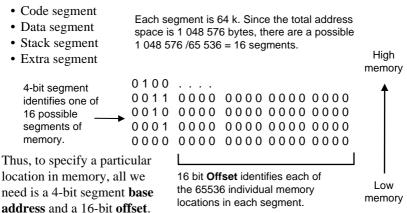

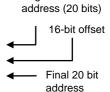

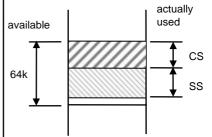

| 2.2.3 Segmented memory                     | 91 |

| 2.2.4 Memory data                          | 92 |

| 2.2.5 Buffers                              | 93 |

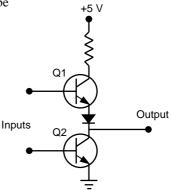

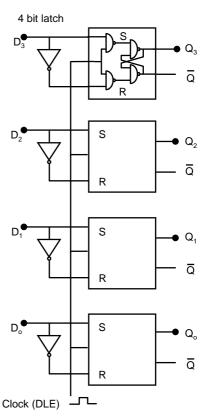

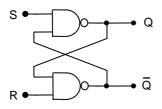

| 2.2.6 Latches                              | 94 |

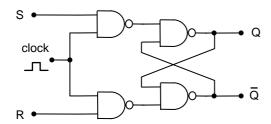

| 2.2.7 Flip-flop                            | 95 |

| 2.2.8 Input/Output (I/O)                   | 06 |

| 2.2.10 Registers       98         2.2.11 ROM       101         2.2.12 Interrupts       102         2.2.13 Memory map       104         2.2.14 Real and protected mode CPU operation       105         2.2.15 Review questions       107         2.2.16 Activities       108         2.3 Assembly language       111         2.3.1 Instruction set       112         2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       119         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       133         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5                                                                                     | 2.2.9 Microprocessor unit (MPU/CPU)       | 97  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|

| 2.2.11 ROM       101         2.2.12 Interrupts       102         2.2.13 Memory map       104         2.2.14 Real and protected mode CPU operation       105         2.2.15 Review questions       107         2.2.16 Activities       106         2.3.1 Instruction set       112         2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       131         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       134         2.4.5 Direct memory access (DMA)       136         2.4.7 Serial port registers and interrupts       136                                                           |                                           | 98  |

| 2.2.13 Memory map       104         2.2.14 Real and protected mode CPU operation       105         2.2.15 Review questions       107         2.2.16 Activities       108         2.3 Assembly language       111         2.3.1 Instruction set       112         2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       118         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       122         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       122         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       133         2.4.2 Input/Output ports       133         2.4.3 Polling       133         2.4.4 Interrupts       133         2.4.5 Direct memory access (DMA)       136         2.4.7 Serial port addresses       138                                                                 |                                           | 101 |

| 2.2.13 Memory map       104         2.2.14 Real and protected mode CPU operation       105         2.2.15 Review questions       107         2.2.16 Activities       108         2.3 Assembly language       111         2.3.1 Instruction set       112         2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       118         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       122         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       122         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       133         2.4.2 Input/Output ports       133         2.4.3 Polling       133         2.4.4 Interrupts       133         2.4.5 Direct memory access (DMA)       136         2.4.7 Serial port addresses       138                                                                 | 2.2.12 Interrupts                         | 102 |

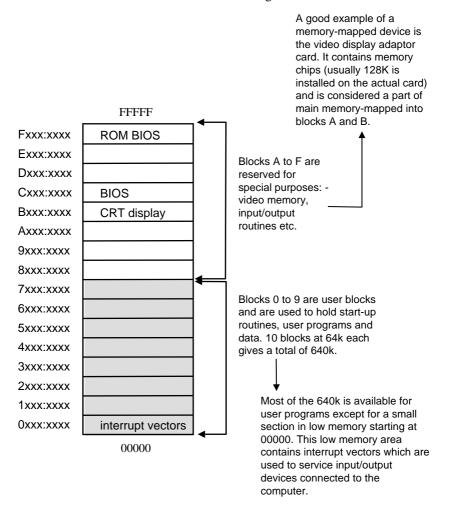

| operation         105           2.2.15 Review questions         107           2.2.16 Activities         108           2.3 Assembly language         111           2.3.1 Instruction set         112           2.3.2 Assembly language         113           2.3.3 Program execution         114           2.3.4 Assembly language program structure         115           2.3.5 Assembler directives         116           2.3.6 Code segment         117           2.3.7 Assembly language shell program         118           2.3.8 Branching         119           2.3.9 Register and immediate addressing         120           2.3.10 Memory addressing         122           2.3.11 Indirect memory addressing         122           2.3.12 Indexed memory addressing         122           2.3.14 Interrupts         124           2.3.15 Review questions         125           2.3.16 Activities         126           2.4.1 Interfacing         131           2.4.2 Input/Output ports         133           2.4.3 Polling         134           2.4.4 Interrupts         135           2.4.5 Direct memory access (DMA)         136           2.4.7 Serial port registers         136 <t< td=""><td></td><td>104</td></t<> |                                           | 104 |

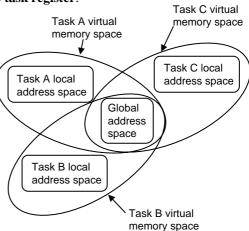

| 2.2.15 Review questions       107         2.2.16 Activities       108         2.3 Assembly language       111         2.3.1 Instruction set       112         2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       118         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       133         2.4.2 Input/Output ports       133         2.4.3 Polling       133         2.4.4 Interrupts       136         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.9 Serial port registers       136         2.4.10 Serial port baud rate       141 </td <td>2.2.14 Real and protected mode CPU</td> <td></td>            | 2.2.14 Real and protected mode CPU        |     |

| 2.2.16 Activities       108         2.3 Assembly language       111         2.3.1 Instruction set       112         2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       118         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       131         2.4.2 Input/Output ports       132         2.4.3 Polling       132         2.4.4 Interrupts       133         2.4.5 Direct memory access (DMA)       136         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port registers       136         2.4.8 Serial port registers and interrupts       146         2.4.10 Serial port operation                                                         |                                           |     |

| 2.3 Assembly language       111         2.3.1 Instruction set       112         2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       119         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       133         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.9 Serial port registers       136         2.4.10 Serial port toperation       142         2.4.11 Serial port operation       142                                                                   | •                                         |     |

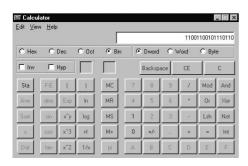

| 2.3.1 Instruction set       112         2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       119         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       131         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.9 Serial port registers       136         2.4.10 Serial port port port registers       140         2.4.12 Parallel printer port       142         2.4.13 Parallel printer port operatio                                                  | 2.2.16 Activities                         | 108 |

| 2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       119         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       122         2.3.11 Indirect memory addressing       123         2.3.12 Indexed memory addressing       123         2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       131         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.9 Serial port registers       136         2.4.10 Serial port baud rate       141         2.4.11 Serial port port port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel printer port operation       145         2.4.15 Re                                                  | 2.3 Assembly language                     | 111 |

| 2.3.2 Assembly language       113         2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       119         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       122         2.3.11 Indirect memory addressing       123         2.3.12 Indexed memory addressing       123         2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       131         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.9 Serial port registers       136         2.4.10 Serial port baud rate       141         2.4.11 Serial port port port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel printer port operation       145         2.4.15 Re                                                  | 2.3.1 Instruction set                     | 112 |

| 2.3.3 Program execution       114         2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       119         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       133         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.5 Direct memory access (DMA)       136         2.4.7 Serial port       137         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel printer port                                                   | 2.3.2 Assembly language                   | 113 |

| 2.3.4 Assembly language program structure       115         2.3.5 Assembler directives       116         2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       120         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       136         2.4.9 Serial port baud rate       141         2.4.10 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel printer port operation       145         2.4.15 Review questions                                                             |                                           | 114 |

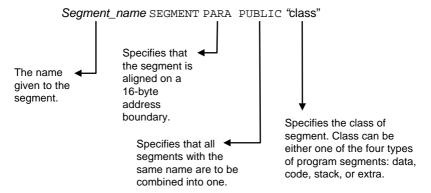

| 2.3.6 Code segment       117         2.3.7 Assembly language shell program       118         2.3.8 Branching       119         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port operation       142         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel printer port operation       145         2.4.15 Review questions       146         2.5.1 Interfacing       14                                                           | 2.3.4 Assembly language program structure | 115 |

| 2.3.7 Assembly language shell program       118         2.3.8 Branching       119         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       133         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port operation       142         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion                                                           | 2.3.5 Assembler directives                | 116 |

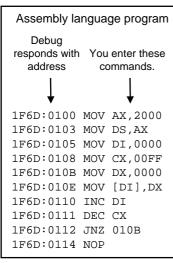

| 2.3.8 Branching       119         2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       123         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port operation       142         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel printer port operation       145         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion                                                          | 2.3.6 Code segment                        | 117 |

| 2.3.9 Register and immediate addressing       120         2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port operation       142         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       148         2.5.3 Resolution and quantisati                                                  | 2.3.7 Assembly language shell program     | 118 |

| 2.3.10 Memory addressing       121         2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port operation       142         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                           | 2.3.8 Branching                           | 119 |

| 2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                     |                                           | 120 |

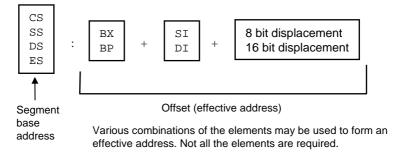

| 2.3.11 Indirect memory addressing       122         2.3.12 Indexed memory addressing       123         2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                     | 2.3.10 Memory addressing                  | 121 |

| 2.3.14 Interrupts       124         2.3.15 Review questions       125         2.3.16 Activities       126         2.4. Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port operation       142         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                       | 2.3.11 Indirect memory addressing         | 122 |

| 2.3.15 Review questions       125         2.3.16 Activities       126         2.4.1 Interfacing       131         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                              | 2.3.12 Indexed memory addressing          | 123 |

| 2.3.16 Activities       126         2.4 Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       139         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                      |                                           | 124 |

| 2.4 Interfacing       131         2.4.1 Interfacing       132         2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       139         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                          | 2.3.15 Review questions                   | 125 |

| 2.4.1 Interfacing.       132         2.4.2 Input/Output ports       133         2.4.3 Polling.       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5. A to D and D to A conversions       147         2.5. 1 Interfacing       148         2.5. 2 The Nyquist criterion       149         2.5. 3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                      | 2.3.16 Activities                         | 126 |

| 2.4.1 Interfacing.       132         2.4.2 Input/Output ports       133         2.4.3 Polling.       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5. A to D and D to A conversions       147         2.5. 1 Interfacing       148         2.5. 2 The Nyquist criterion       149         2.5. 3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                      | 2.4 Interfacing                           | 131 |

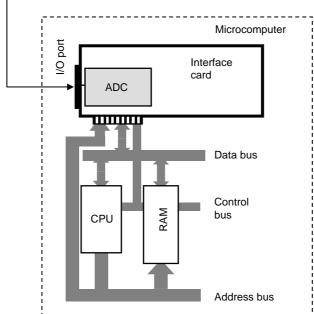

| 2.4.2 Input/Output ports       133         2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                |                                           | 132 |

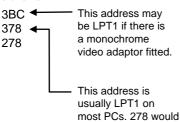

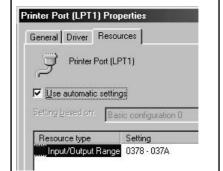

| 2.4.3 Polling       134         2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       139         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           | 133 |

| 2.4.4 Interrupts       135         2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       139         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           | 134 |

| 2.4.5 Direct memory access (DMA)       136         2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       139         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           | 135 |

| 2.4.6 Serial port       137         2.4.7 Serial port addresses       138         2.4.8 Serial port registers       139         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                           | 136 |

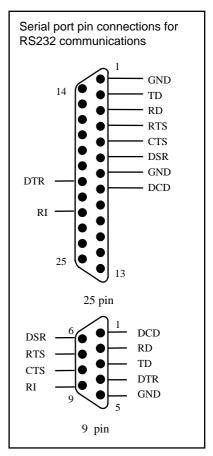

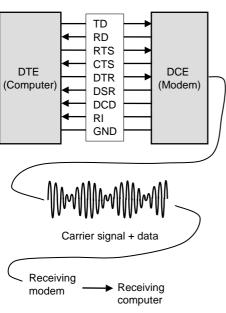

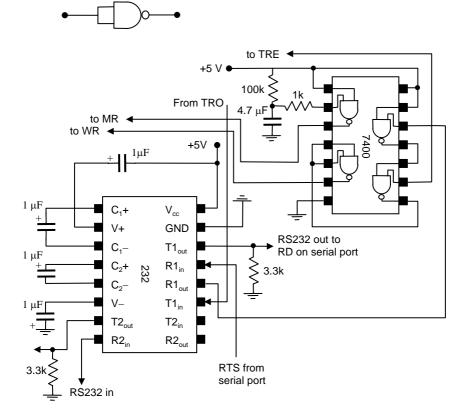

| 2.4.7 Serial port addresses       138         2.4.8 Serial port registers       139         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           | 137 |

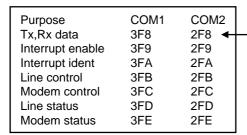

| 2.4.8 Serial port registers       138         2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           | 138 |

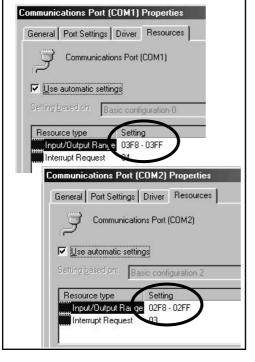

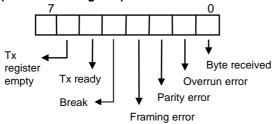

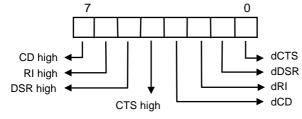

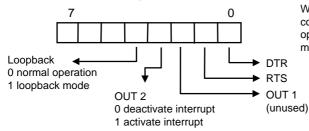

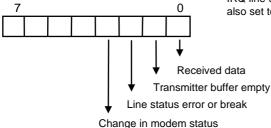

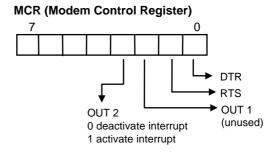

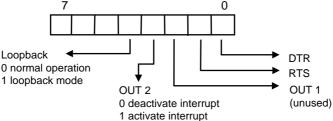

| 2.4.9 Serial port registers and interrupts       140         2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.4.8 Serial port registers               | 139 |

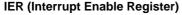

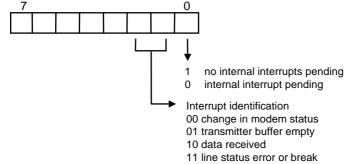

| 2.4.10 Serial port baud rate       141         2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           | 140 |

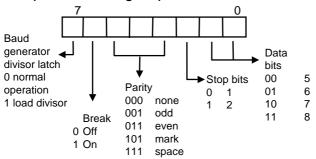

| 2.4.11 Serial port operation       142         2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           | 141 |

| 2.4.12 Parallel printer port       143         2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                           | 142 |

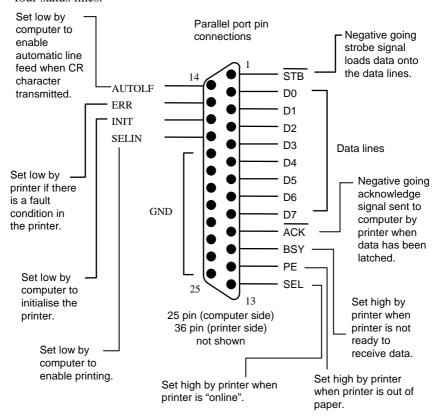

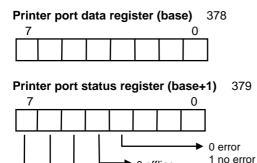

| 2.4.13 Parallel port registers       144         2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           | 143 |

| 2.4.14 Parallel printer port operation       145         2.4.15 Review questions       146         2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                           | 144 |

| 2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           | 145 |

| 2.5 A to D and D to A conversions       147         2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.4.15 Review questions                   | 146 |

| 2.5.1 Interfacing       148         2.5.2 The Nyquist criterion       149         2.5.3 Resolution and quantisation noise       150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           | 147 |

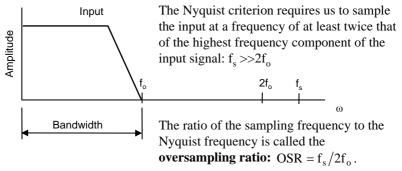

| 2.5.2 The Nyquist criterion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |     |

| 2.5.3 Resolution and quantisation noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | S .                                       | _   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                           | _   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.5.4 Oversampling                        | 151 |

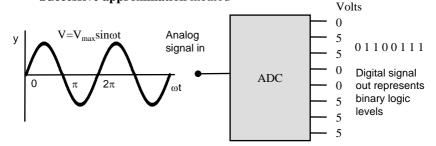

| 2.5.5 Analog to digital converters    | 152<br>153 |

|---------------------------------------|------------|

| 2.5.7 ADC (successive approximation)  | 154        |

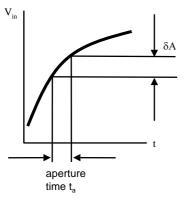

| 2.5.8 Aperture error                  | 155        |

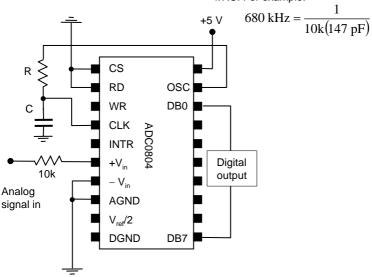

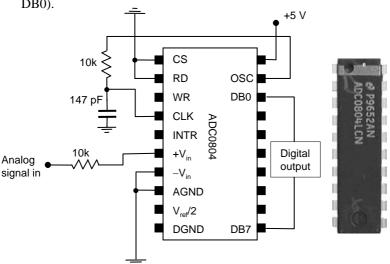

| 2.5.9 ADC08xx chip                    | 156        |

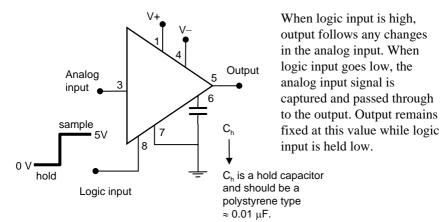

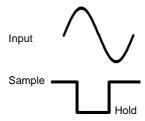

| 2.5.10 Sample-and-hold                | 157        |

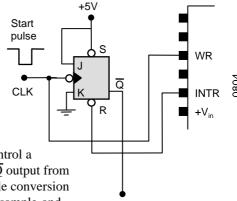

| 2.5.11 Sample-and-hold control        | 158        |

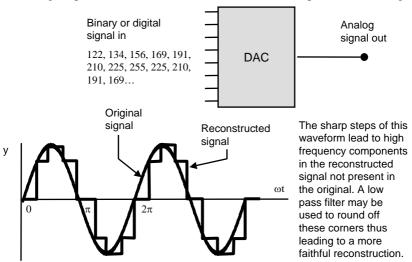

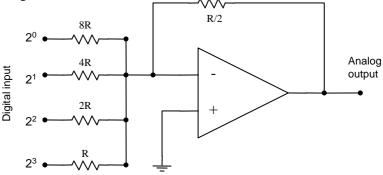

| 2.5.12 Digital to analog conversion   | 159        |

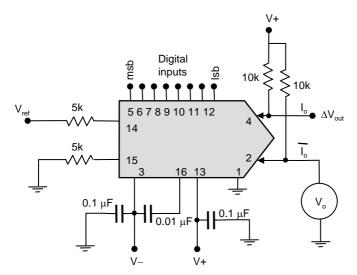

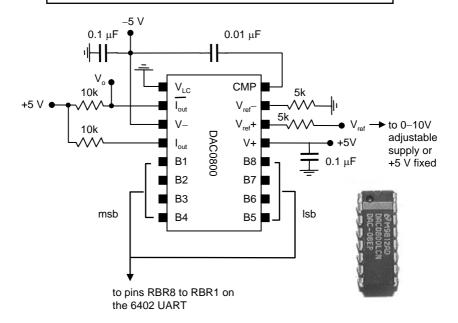

| 2.5.13 DAC0800                        | 160        |

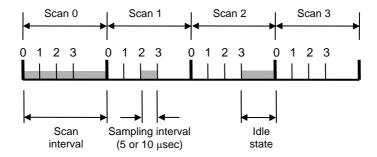

| 2.5.14 Data acquisition board         | 161        |

| 2.5.15 Review questions               | 162        |

| 2.6 Data communications               | 163        |

| 2.6.1 Communications                  | 164        |

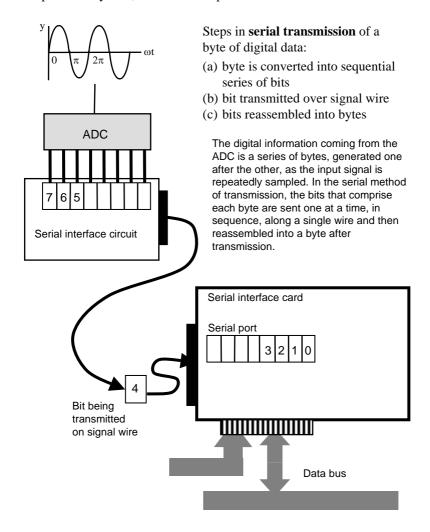

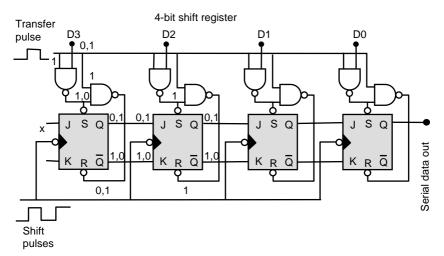

| 2.6.2 Byte to serial conversion       | 165        |

| 2.6.3 RS232 interface                 | 166        |

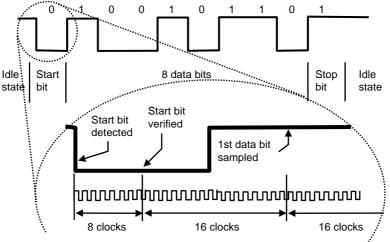

| 2.6.4 Synchronisation                 | 167        |

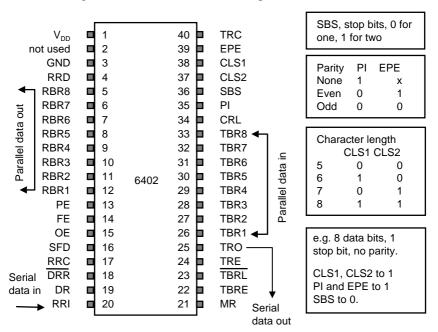

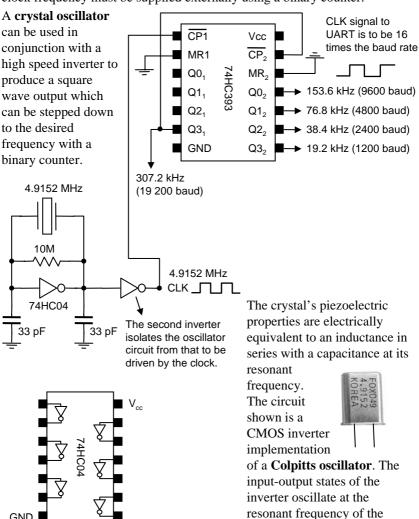

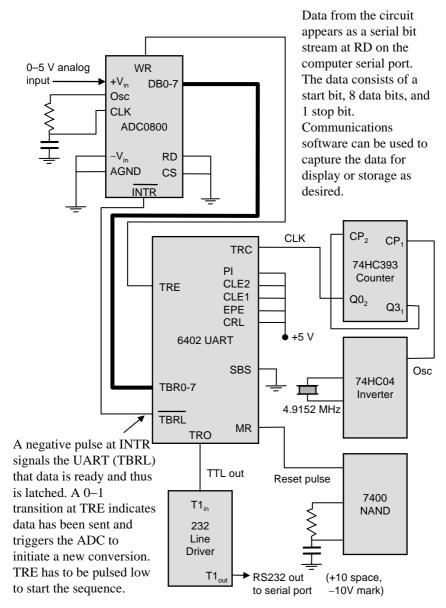

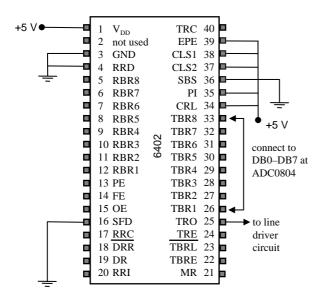

| 2.6.5 UART (6402)                     | 168        |

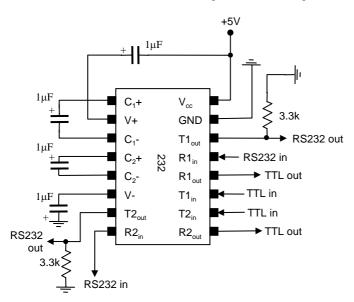

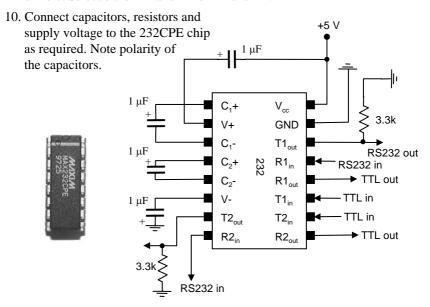

| 2.6.7 Line drivers                    | 170        |

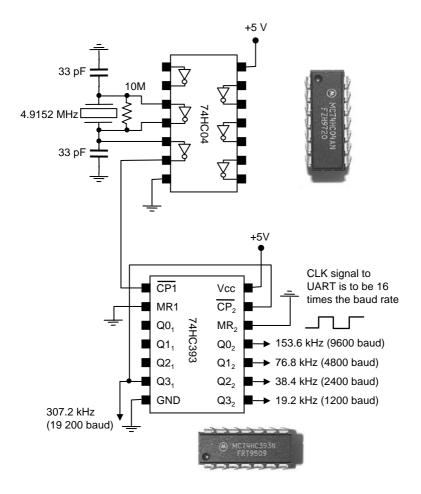

| 2.6.8 UART clock                      | 171        |

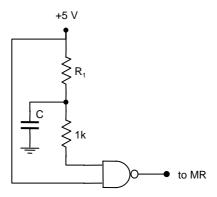

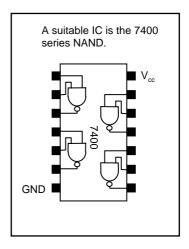

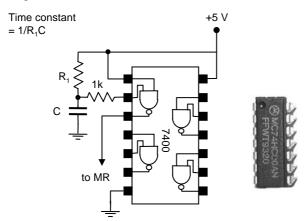

| 2.6.9 UART Master Reset               | 172        |

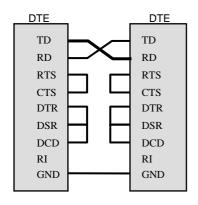

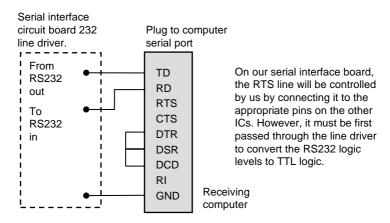

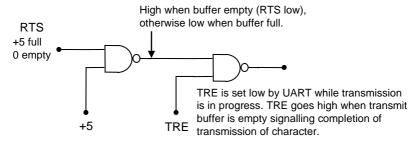

| 2.6.10 Null modem                     | 173        |

| 2.6.11 Serial port BIOS services      | 174        |

| 2.6.12 Serial port operation in BASIC | 175<br>176 |

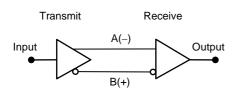

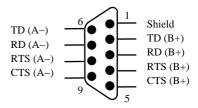

| 2.6.14 RS485                          | 176        |

| 2.6.15 GPIB                           | 177        |

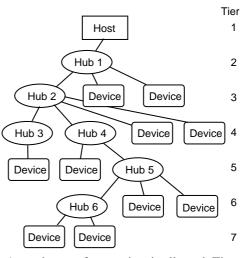

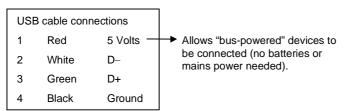

| 2.6.16 USB                            | 170        |

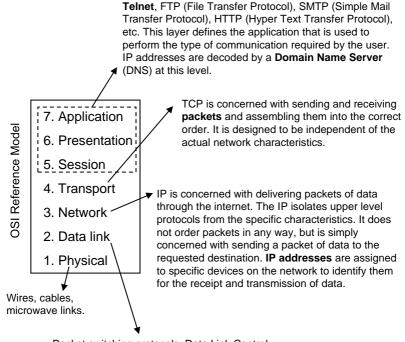

| 2.6.17 TCP/IP                         | 181        |

| 2.6.18 Review questions               | 182        |

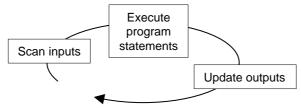

| 2.7 Programmable logic controllers    | 183        |

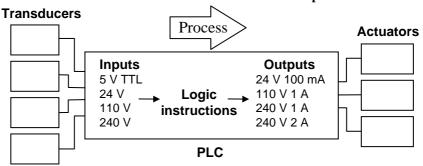

| 2.7.1 Programmable logic controllers  | 184        |

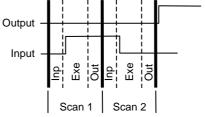

| 2.7.2 Timing                          | 185        |

| 2.7.3 Functional components           | 186        |

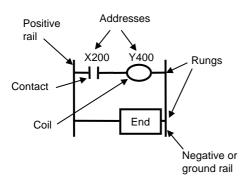

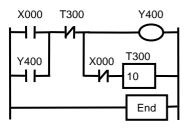

| 2.7.4 Programming                     | 187        |

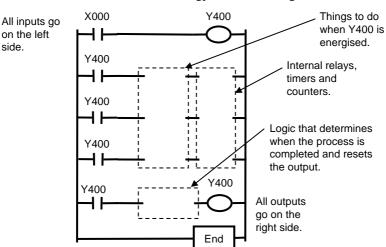

| 2.7.5 Ladder logic diagrams           | 188        |

| 2.7.6 PLC specifications              | 190        |

| 2.7.7 Review questions                | 191        |

| 2.8 Data acquisition project          | 192        |

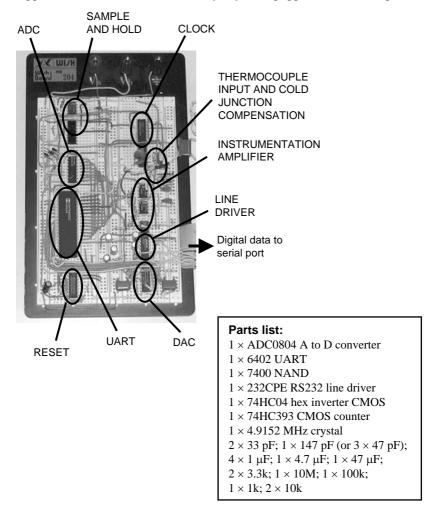

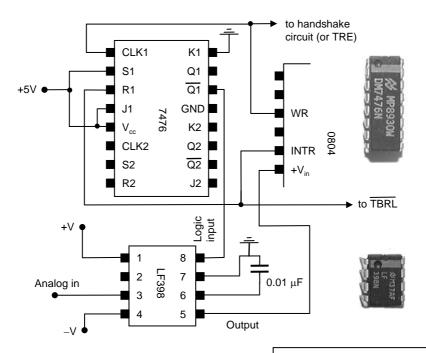

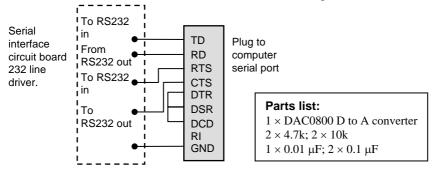

| 2.8.1 Serial data acquisition system  | 193        |

| 2.8.2 Circuit construction            | 195        |

| 2.8.3 Programming                     | 201        |

| 2.8.4 Sample-and-hold                 | 206        |

| 2.8.5 Digital to analog system        | 208        |

| Part 3: Signal processing             |            |

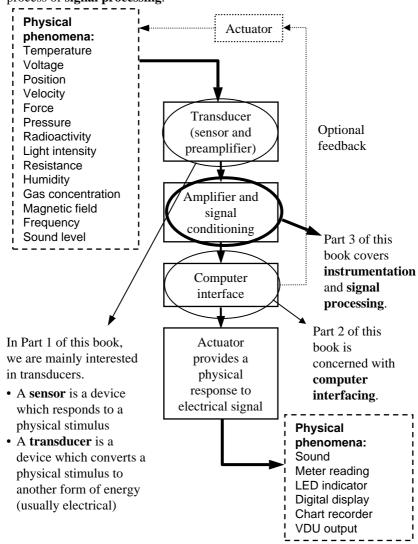

| 3.0 Signal processing                                | 212 |

|------------------------------------------------------|-----|

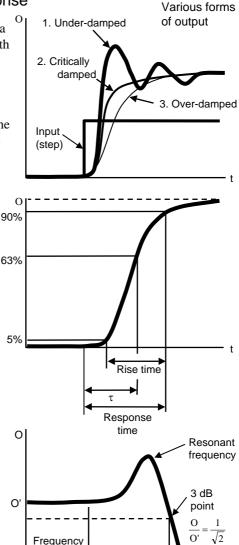

| 3.1 Transfer function                                | 213 |

| 3.1.1 Instrumentation                                | 214 |

| 3.1.2 Transfer function                              | 215 |

| 3.1.3 Transforms                                     | 216 |

| 3.1.4 Laplace transform                              | 217 |

| 3.1.5 Operator notation                              | 218 |

| 3.1.6 Differential operator                          | 219 |

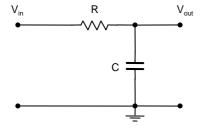

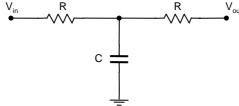

| 3.1.7 Integrator passive                             | 220 |

| 3.1.8 Differentiator passive                         | 221 |

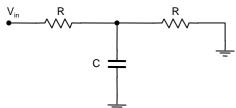

| 3.1.9 Transfer impedance                             | 222 |

| 3.1.10 Review questions                              | 223 |

| 3.1.11 Activities                                    | 224 |

| 3.2 Active filters                                   | 227 |

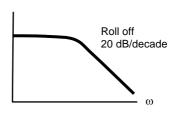

| 3.2.1 Filters                                        | 228 |

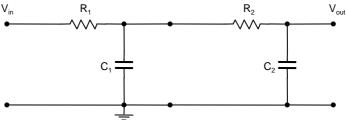

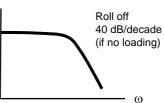

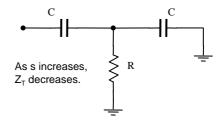

| 3.2.2 T -network filters                             | 229 |

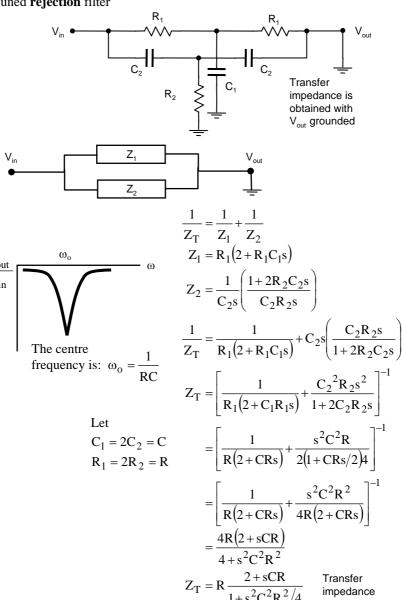

| 3.2.3 Twin-T filter                                  | 230 |

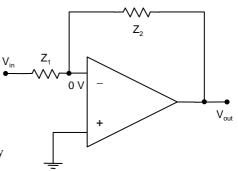

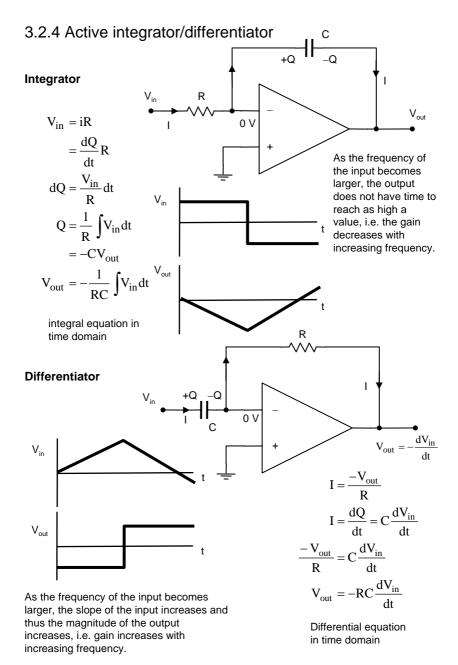

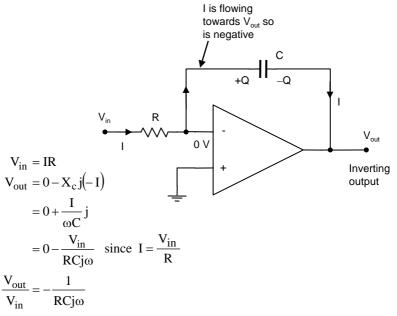

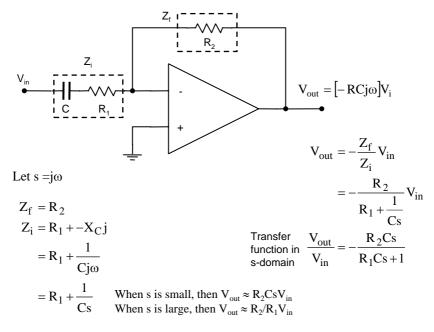

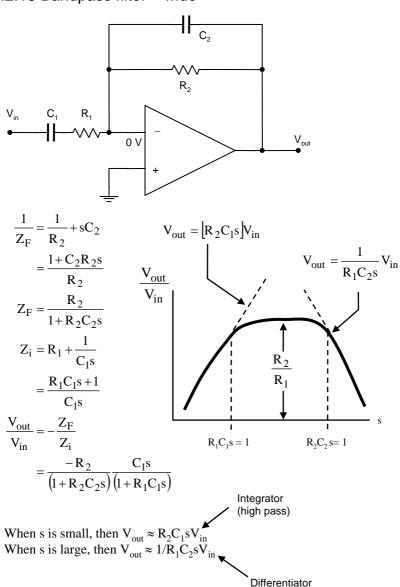

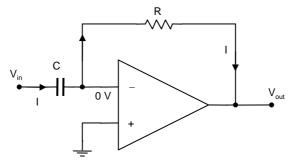

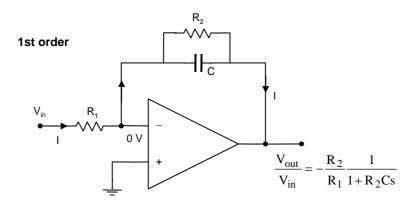

| 3.2.4 Active integrator/differentiator               | 231 |

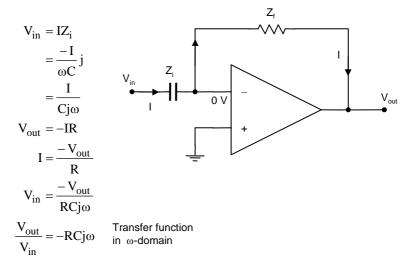

| 3.2.5 Integrator transfer function                   | 232 |

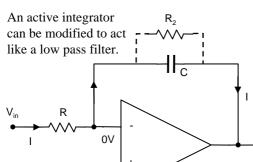

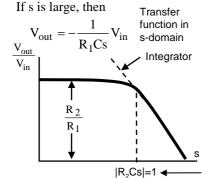

| 3.2.6 Low pass filter active                         | 233 |

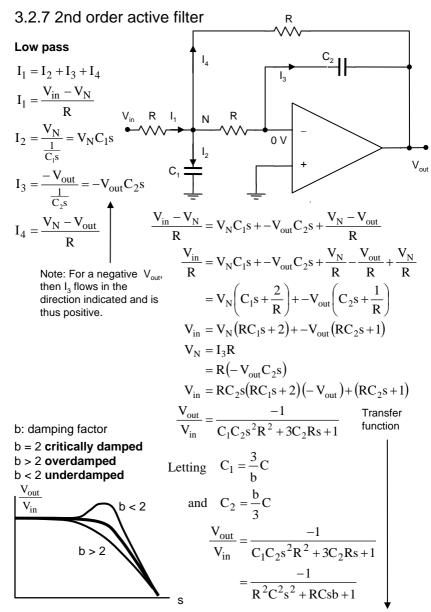

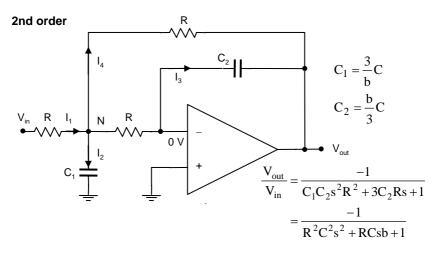

| 3.2.7 2nd order active filter                        | 234 |

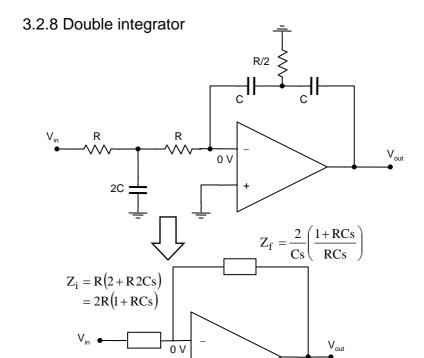

| 3.2.8 Double integrator                              | 235 |

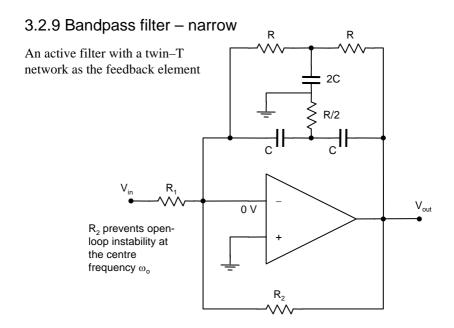

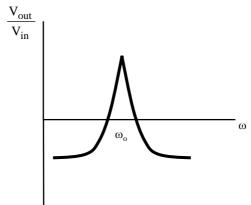

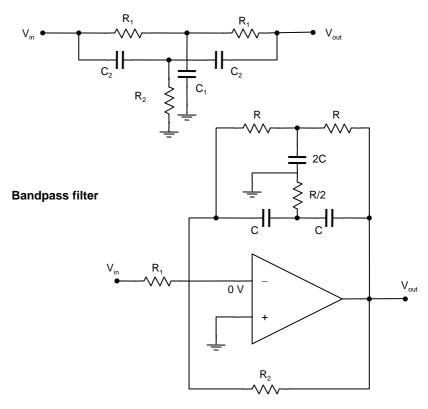

| 3.2.9 Bandpass filter narrow                         | 236 |

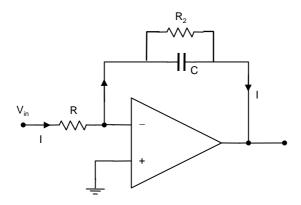

| 3.2.10 Differentiator transfer function              | 237 |

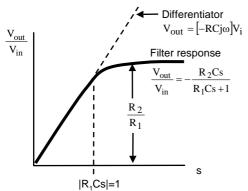

| 3.2.11 High pass filter active                       | 238 |

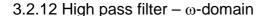

| 3.2.12 High pass filter w domain                     | 239 |

| 3.2.13 Bandpass filter wide                          | 240 |

| 3.2.14 Voltage gain and dB                           | 241 |

| 3.2.15 Review questions                              | 242 |

| 3.2.16 Activities                                    | 244 |

| 3.3 Instrumentation amplifier                        | 246 |

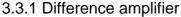

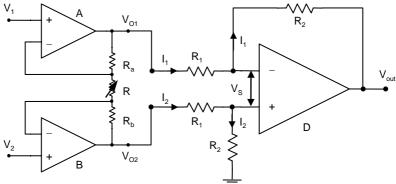

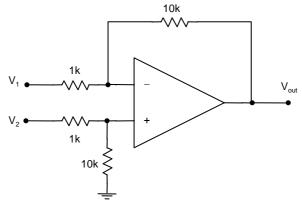

| 3.3.1 Difference amplifier                           | 247 |

| 3.3.2 CMRR                                           | 248 |

| 3.3.3 Difference amplifier with voltage              |     |

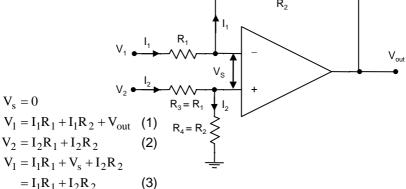

| follower inputs                                      | 249 |

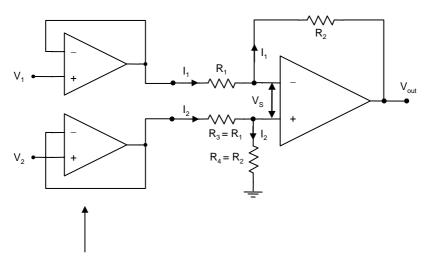

| 3.3.4 Difference amplifier with cross-coupled inputs | 250 |

| 3.3.5 CMRR cross-coupled inputs                      | 251 |

| 3.3.6 Instrumentation amplifier                      | 252 |

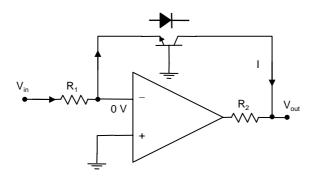

| 3.3.7 Log amplifier                                  | 253 |

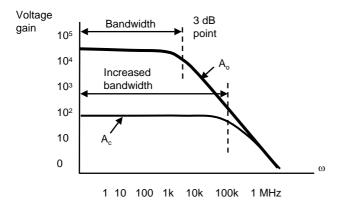

| 3.3.8 Op-amp frequency response                      | 254 |

| 3.3.9 Review questions                               | 255 |

| 3.3.10 Activities                                    | 257 |

|                                                      |     |

| 3.4 Noise                                            | 261 |

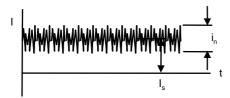

| 3.4.1 Intrinsic noise                                | 262 |

| 3.4.2 Environmental noise           | 203 |

|-------------------------------------|-----|

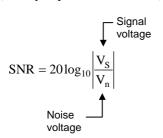

| 3.4.3 Signal-to-noise ratio         | 264 |

| 3.4.4 Optical detectors             | 265 |

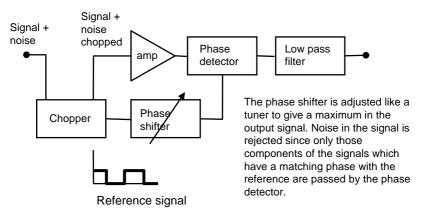

| 3.4.5 Lock-in amplifier             | 266 |

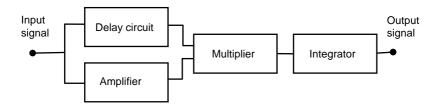

| 3.4.6 Correlation                   | 267 |

| 3.4.7 Review questions              | 268 |

| 3.5 Digital signal processing       | 269 |

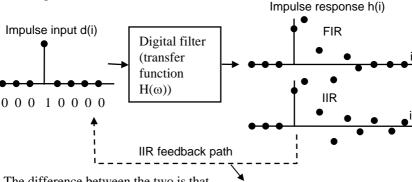

| 3.5.1 Digital filters               | 270 |

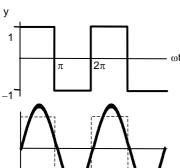

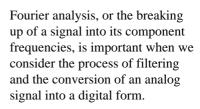

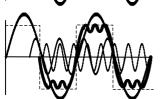

| 3.5.2 Fourier series                | 271 |

| 3.5.3 Fourier transform             | 272 |

| 3.5.4 Sampling                      | 273 |

| 3.5.5 Discrete Fourier transform    | 274 |

| 3.5.6 Filtering                     | 275 |

| 3.5.7 Digital filtering (domain)    | 276 |

| 3.5.8 Convolution                   | 277 |

| 3.5.9 Discrete convolution          | 278 |

| 3.5.10 Digital filtering (t-domain) | 279 |

| 3.5.11 Example                      | 280 |

| 3.5.12 Smoothing transfer function  | 281 |

| 3.5.13 Review questions             | 282 |

| 3.5.14 Activities                   | 283 |

| ndex                                | 286 |

| Further reading                     |     |

| Parts lists for activities          | 295 |

# **Preface**

The overall aim of this book is to present transducer devices, computer interfacing and instrumentation electronics in a succinct and memorable fashion. The book combines physics, computer science and electrical engineering in a science/engineering context. Starting from the transfer of physical phenomena to electrical signals, the book presents a comprehensive treatment of computer interfacing and finishes with signal conditioning, data analysis and digital filtering. The book covers a wide scope but contains sufficient detail to allow a practical application of the theory. Detailed explanations are given, even of the most difficult of concepts. The review problems offer a level of complexity which provides sufficient challenge to impart a sense of achievement upon their completion. The accompanying project work reinforces the theoretical work while allowing the reader to gain the satisfaction and experience of actually constructing a working interfacing circuit that can be used on any personal computer with a serial port. The book will be useful for students who are new to the subject, and will serve as a handy reference for experienced engineers who wish to refresh their knowledge of a particular topic.

In writing this book, I was assisted and encouraged by many colleagues. In particular, I acknowledge the contributions of Alec Bendeli, Stephen Buck, Bob Graves, Walter Kalceff, Les Kirkup, Geoff Smith, Paul Walker, my colleagues at the University of Technology, Sydney, the staff of the CSIRO Division of Telecommunications and Industrial Physics, and all my former students. My sincere thanks to my wife and family for their unending encouragement and support. Finally, I thank Matthew Deans, Jodi Burton and the editorial and production teams at Newnes for their very professional and helpful approach to the whole publication process.

Tony Fischer-Cripps, Killarney Heights, Australia, 2002

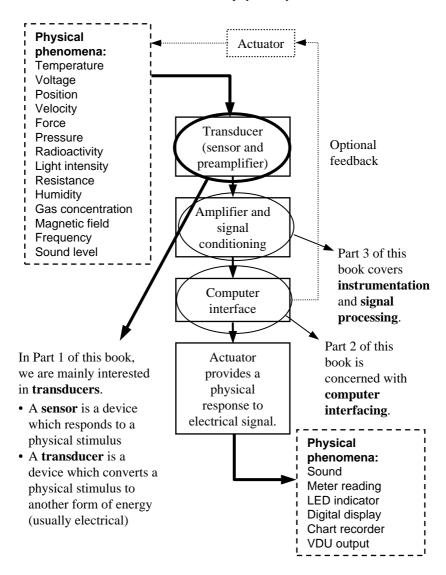

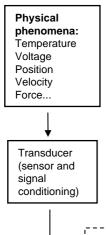

#### 1.0 Transducers

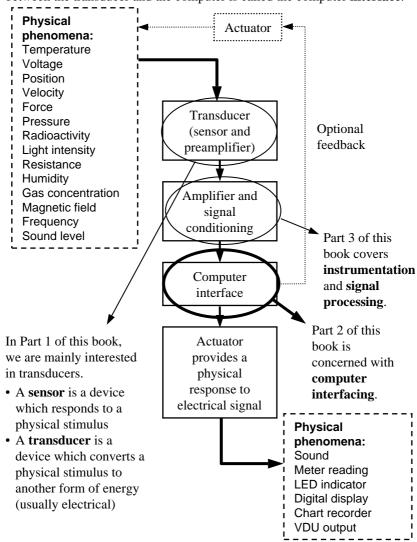

A measurement system is concerned with the representation of one physical phenomenon by another. The purpose of the measurement system is for the measurement and control of a physical system.

# 1.1.1 Transducers

Of most interest are the physical properties and performance characteristics of a transducer. Some examples are given below:

| Property       | Method of measurement                                                      |

|----------------|----------------------------------------------------------------------------|

| Strain         | Strain gauge, a resistive transducer whose resistance changes with length. |

| Temperature    | Resistance thermometer, thermocouple, thermister, thermopile.              |

| Humidity       | Resistance change of hygroscopic material.                                 |

| Pressure       | Movement of the end of a coiled tube under pressure.                       |

| Voltage        | Moving coil in a magnetic field.                                           |

| Radioactivity  | Electrical pulses resulting from ionisation of gas at low pressure.        |

| Magnetic field | Deflection of a current carrying wire.                                     |

# Performance characteristics

| Static                                               | Dynamic                                                                                                   | Environmental         |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| Sensitivity                                          | Response time                                                                                             | Operating temperature |  |  |

| Zero offset                                          | Damping                                                                                                   | range                 |  |  |

| Linearity                                            | Natural frequency                                                                                         | Orientation           |  |  |

| Range                                                | Frequency response                                                                                        | Vibration/shock       |  |  |

| Span                                                 |                                                                                                           |                       |  |  |

| Resolution                                           | A consideration of these characteristics influences the                                                   |                       |  |  |

| Threshold                                            | choice of transducer for a particular application.  Further characteristics which are often important are |                       |  |  |

| Hysteresis                                           |                                                                                                           |                       |  |  |

| Repeatability                                        |                                                                                                           |                       |  |  |

| and safety aspects of the device as well as cost and |                                                                                                           |                       |  |  |

availability of service.