موقع عالم الإلكترون.... موقع إلكتروني متخصص في علوم الهندسة التكنلوجية واختصاصاتها المختلفة

مكتبة عالم الإلكترون 4electron.com

إلى قارئ هذا الكتاب ، تحية طيبة وبعد ...

لقد أصبحنا نعيش في عالم يعج بالأبحاث والكتب والمعلومات، وأصبح العلم معياراً حقيقياً لتفاضل الأمم والدول والمؤسسات والأشخاص على حدِّ سواء، وقد أمسى بدوره حلاً شبه وحيد لأكثر مشاكل العالم حدة وخطورة، فالبيئة تبحث عن حلول، وصحة الإنسان تبحث عن حلول، والموارد التي تشكل حاجة أساسية للإنسان تبحث عن حلول كذلك، والطاقة والغذاء والماء جميعها تحديات يقف العلم في وجهها الآن ويحاول أن يجد الحلول لها. فأين نحن من هذا العلم ؟ وأين هو منا؟

نسعى في موقع عالم الإلكترون <u>www.4electron.com</u> لأن نوفر بين أيدي كل من حمل على عاتقه مسيرة درب تملؤه التحديات ما نستطيع من أدوات تساعده في هذا الدرب، من مواضيع علمية، ومراجع أجنبية بأحدث إصداراتها، وساحات لتبادل الآراء والأفكار العلمية والمرتبطة بحياتنا الهندسية، وشروح لأهم برمجيات الحاسب التي تتداخل مع تطبيقات الحياة الأكاديمية والعملية، ولكننا نتوقع في نفس الوقت أن نجد بين الطلاب والمهندسين والباحثين من يسعى مثلنا لتحقيق النفع والفائدة للجميع، ويحلم أن يكون عضواً في مجتمع يساهم بتحقيق بيئة خصبة للمواهب والإبداعات والتألق، فهل تحلم بذلك ؟

حاول أن تساهم بفكرة، بومضة من خواطر تفكيرك العلمي، بفائدة رأيتها في إحدى المواضيع العلمية، بجانب مضيء لمحته خلف ثنايا مفهوم هندسي ما. تأكد بأنك ستلتمس الفائدة في كل خطوة تخطوها، وترى غيرك يخطوها معك ...

أخي القارئ، نرجو أن يكون هذا الكتاب مقدمة لمشاركتك في عالمنا العلمي التعاوني، وسيكون موقعكم عالم الإلكترون <u>ww.4electron.com</u> بكل الإمكانيات المتوفرة لديه جاهزاً على الدوام لأن يحقق البيئة والواقع الذي يبحث عنه كل باحث أو طالب في علوم الهندسة، ويسعى فيه للإفادة كل ساع ، فأهلاً وسهلاً بكم .

مع تحيات إدارة الموقع وفريق عمله

www.4electron.com

موقع عالم الإلكترون

www.4electron.com

# Microcontroller Programming

# **The Microchip PIC®**

# Julio Sanchez Maria P. Canton

# **Microcontroller Programming** The Microchip PIC®

# Microcontroller Programming The Microchip PIC®

# **Julio Sanchez**

Minnesota State University, Mankato

Maria P. Canton South Central College, North Mankato, Minnesota

CRC Press is an imprint of the Taylor & Francis Group, an informa business

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2007 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number-10: 0-8493-7189-9 (Hardcover) International Standard Book Number-13: 978-0-8493-7189-9 (Hardcover)

This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

No part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http:// www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC) 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

# Table of Contents

| Pre  | face                                                       | XV       |

|------|------------------------------------------------------------|----------|

| Chap | ter 1 - Basic Electronics                                  | 1        |

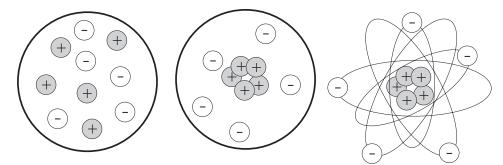

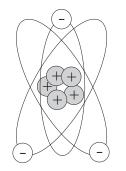

| 1.0  | The Atom                                                   | 1        |

| 1.1  | Isotopes and Ions                                          | 2        |

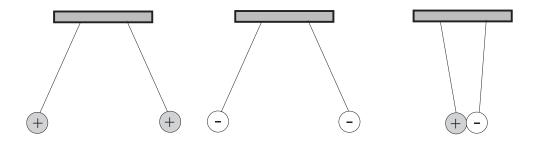

| 1.2  | Static Electricity                                         | 3        |

|      | Electrical Charge                                          | 4        |

|      | 1.3.1 Voltage                                              | 4        |

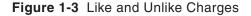

|      | 1.3.2 Current                                              | 4        |

|      | 1.3.3 Power                                                | 5        |

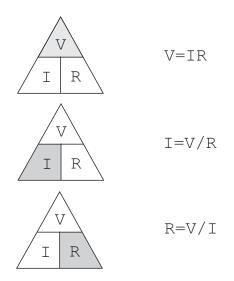

|      | 1.3.4 Ohm's Law                                            | 5        |

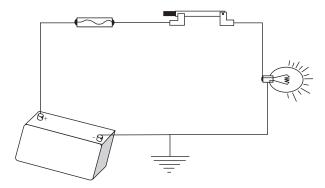

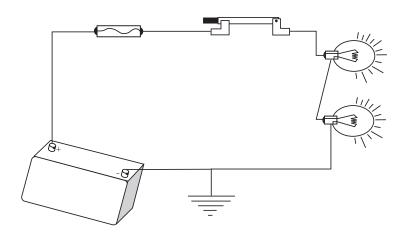

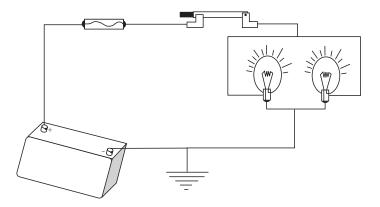

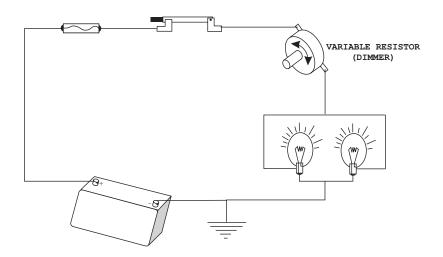

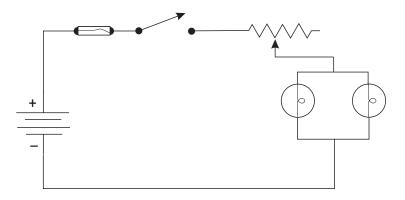

| 1.4  | Electrical Circuits                                        | 6        |

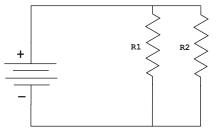

|      | 1.4.1 Types of Circuits                                    | 6        |

| 1.5  | Circuit Elements                                           | 8        |

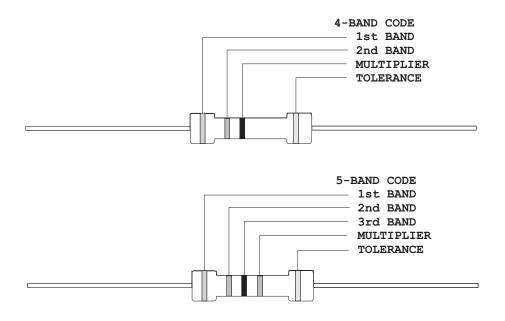

|      | 1.5.1 Resistors                                            | 9        |

|      | 1.5.2 Revisiting Ohm's Law                                 | 9        |

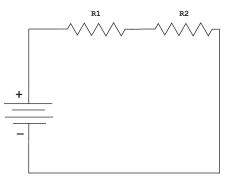

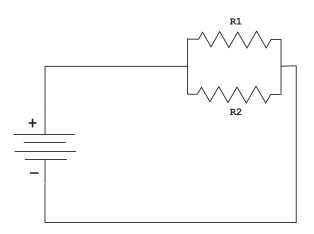

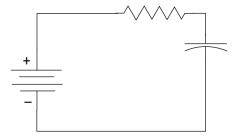

|      | 1.5.3 Resistors in Series and Parallel<br>1.5.4 Capacitors | 10<br>12 |

|      | 1.5.5 Capacitors in Series and in Parallel                 | 12       |

|      | 1.5.6 Inductors                                            | 14       |

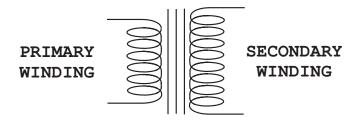

|      | 1.5.7 Transformers                                         | 15       |

| 1.6  | Semiconductors                                             | 15       |

|      | 1.6.1 Integrated Circuits                                  | 16       |

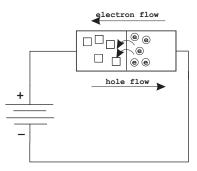

|      | 1.6.2 Semiconductor Electronics                            | 16       |

|      | 1.6.3 P-Type and N-Type Silicon                            | 17       |

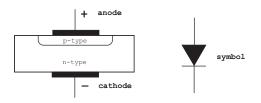

|      | 1.6.4 The Diode                                            | 17       |

| Chap | ter 2 - Number Systems                                     | 19       |

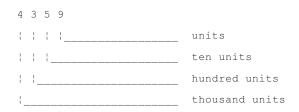

| 20   | Counting                                                   | 19       |

| 2.0  | 2.0.1 The Tally System                                     | 19       |

|      | 2.0.2 Roman Numerals                                       | 20       |

| 2.1  | The Origins of the Decimal System                          | 20       |

| -    | 2.1.1 Number Systems for Digital-Electronics               | 22       |

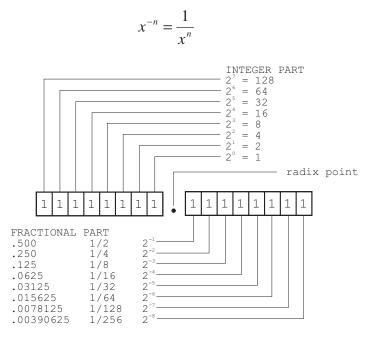

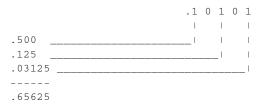

|      | 2.1.2 Positional Characteristics                           | 22       |

|      | 2.1.3 Radix or Base of a Number System                     | 23       |

|      |                                                            |          |

| 2.2  | Types of Numbers<br>2.2.1 Whole Numbers<br>2.2.2 Signed Numbers<br>2.2.3 Rational, Irrational, and Imaginary Numbers                       | 23<br>24<br>24<br>24 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

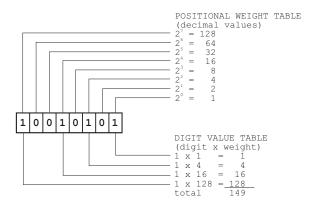

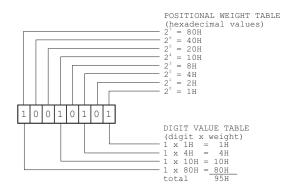

| 2.3  | Radix Representations<br>2.3.1 Decimal versus Binary Numbers<br>2.3.2 Hexadecimal and Octal                                                | 25<br>25<br>26       |

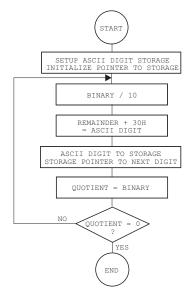

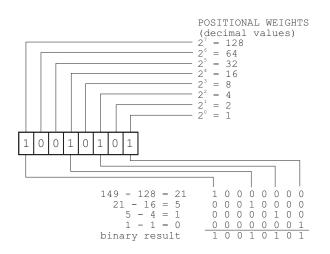

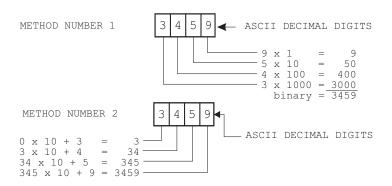

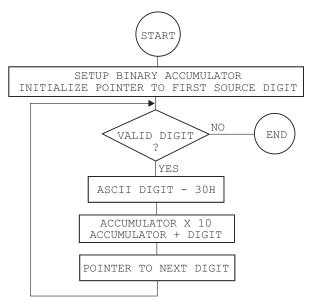

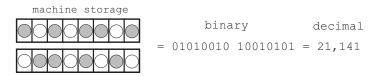

| 2.4  | Number System Conversions<br>2.4.1 Binary-to-ASCII-Decimal<br>2.4.2 Binary-to-Hexadecimal Conversion<br>2.4.3 Decimal-to-Binary Conversion | 27<br>28<br>29<br>29 |

| Chap | ter 3 - Data Types and Data Storage                                                                                                        | 33                   |

| 3.0  | Electronic-Digital Machines                                                                                                                | 33                   |

| 3.1  | Character Representations                                                                                                                  | 33                   |

|      | 3.1.1 ASCII                                                                                                                                | 34                   |

|      | 3.1.2 EBCDIC and IBM<br>3.1.3 Unicode                                                                                                      | 36<br>36             |

| 3.2  | Storage and Encoding of Integers                                                                                                           | 37                   |

|      | 3.2.1 Signed and Unsigned Representations                                                                                                  | 37                   |

|      | 3.2.2 Word Size                                                                                                                            | 38                   |

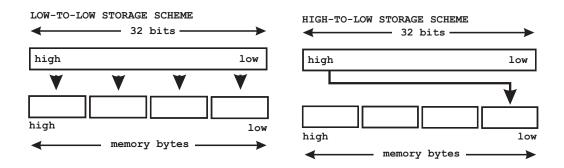

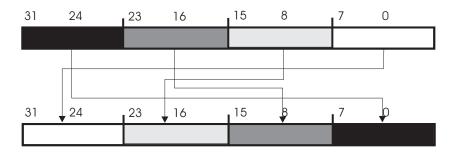

|      | 3.2.3 Byte Ordering<br>3.2.4 Sign-Magnitude Representation                                                                                 | 39<br>40             |

|      | 3.2.5 Radix Complement Representation                                                                                                      | 41                   |

| 3.3  | Encoding of Fractional Numbers                                                                                                             | 44                   |

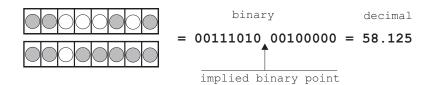

|      | 3.3.1 Fixed-Point Representations                                                                                                          | 45                   |

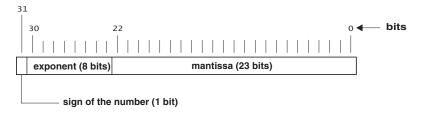

|      | 3.3.2 Floating-Point Representations                                                                                                       | 46                   |

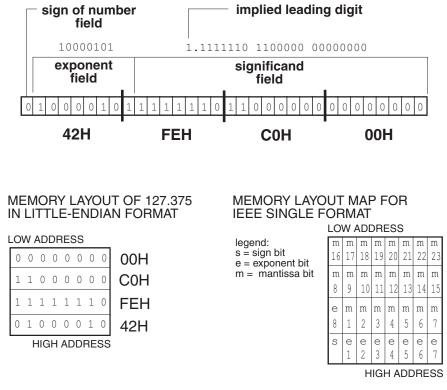

|      | 3.3.3 Standardized Floating-Point Representations<br>3.3.4 IEEE 754 Single Format                                                          | 47<br>48             |

|      | 3.3.5 Encoding and Decoding Floating-Point Numbers                                                                                         | 50                   |

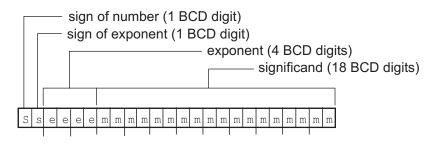

| 3.4  | Binary-Coded Decimals (BCD)                                                                                                                | 51                   |

|      | 3.4.1 Floating-Point BCD                                                                                                                   | 52                   |

| Chap | ter 4 - Digital Logic, Arithmetic, and Conversions                                                                                         | 55                   |

| 4.0  | Microcontroller Logic and Arithmetic                                                                                                       | 55                   |

|      | 4.0.1 CPU Flags                                                                                                                            | 55                   |

|      | 4.0.2 Word Size                                                                                                                            | 56                   |

| 4.1  | Logical Instructions<br>4.1.1 Logical AND                                                                                                  | 56<br>57             |

|      | 4.1.2 Logical OR                                                                                                                           | 57                   |

|      | 4.1.3 Logical XOR                                                                                                                          | 57                   |

|      | 4.1.4 Logical NOT                                                                                                                          | 58                   |

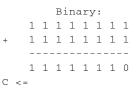

| 4.2  | Microcontroller Arithmetic                                                                                                                 | 58                   |

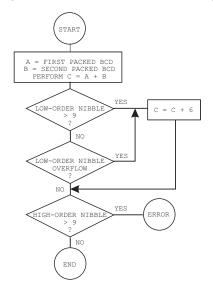

|      | 4.2.1 Unsigned and Two's Complement Arithmetic<br>4.2.2 Operations on Decimal Numbers                                                      | 58<br>60             |

| 12   | Bit Manipulations and Auxiliary Operations                                                                                                 | 62                   |

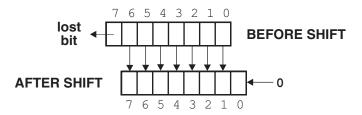

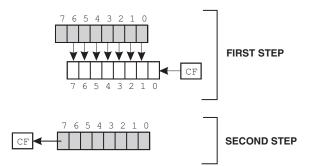

| 4.5  | 4.3.1 Bit Shift and Rotate                                                                                                                 | 62                   |

|      | 4.3.2 Comparison Operations                                                                                                                | 63                   |

|      | 4.3.3 Other Support Operations                                                                                                             | 63                   |

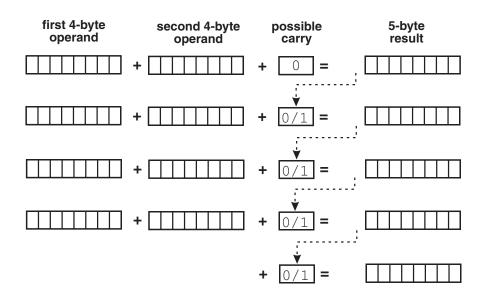

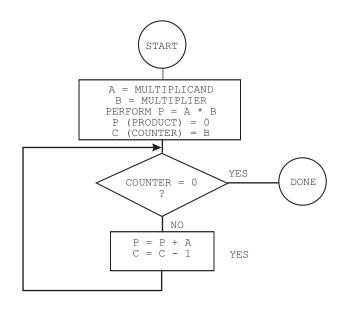

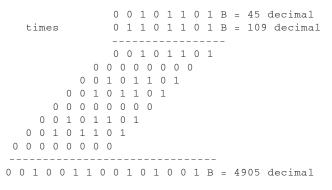

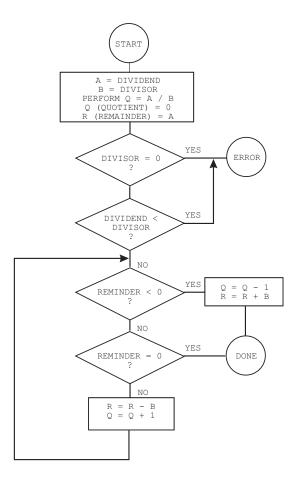

| 4.4  | Unsigned Binary Arithmetic<br>4.4.1 Multi-byte Unsigned Addition<br>4.4.2 Unsigned Multiplication<br>4.4.3 Unsigned Division                                                                                                                                                                                | 64<br>64<br>65<br>67                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

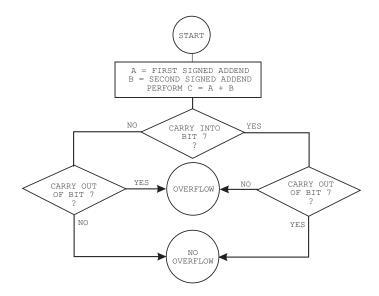

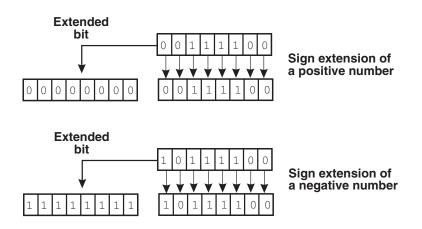

| 4.5  | <ul> <li>Signed Binary Arithmetic</li> <li>4.5.1 Overflow Detection in Signed Arithmetic</li> <li>4.5.2 Sign Extension Operations</li> <li>4.5.3 Multi-byte Signed Operations</li> </ul>                                                                                                                    | 67<br>69<br>70<br>71                   |

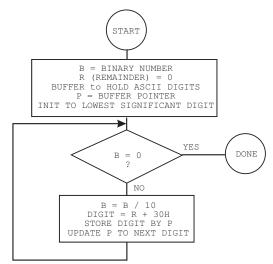

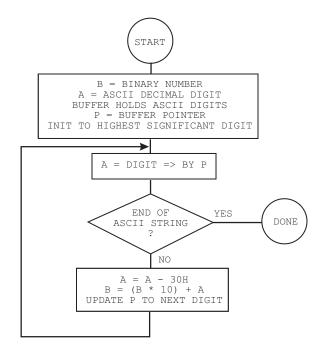

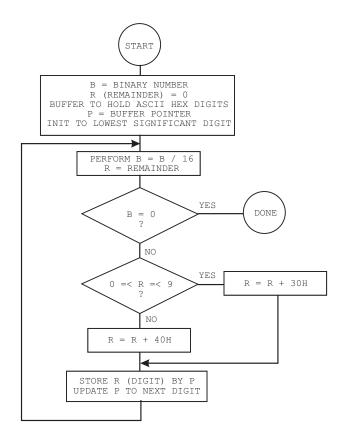

| 4.6  | <ul> <li>Data Format Conversions</li> <li>4.6.1 BCD Digits to ASCII Decimal</li> <li>4.6.2 Unsigned Binary to ASCII Decimal Digits</li> <li>4.6.3 ASCII Decimal String to Unsigned Binary</li> <li>4.6.4 Unsigned Binary to ASCII Hexadecimal Digits</li> <li>4.6.6 Signed Numerical Conversions</li> </ul> | 72<br>72<br>73<br>73<br>73<br>75<br>76 |

| Chap | oter 5 - Circuits and Logic Gates                                                                                                                                                                                                                                                                           | 77                                     |

| 5.0  | Digital Circuits                                                                                                                                                                                                                                                                                            | 77                                     |

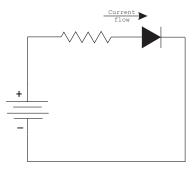

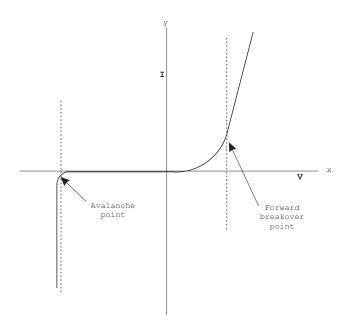

| 5.1  | The Diode Revisited                                                                                                                                                                                                                                                                                         | 78                                     |

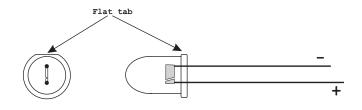

|      | 5.1.1 The Light-Emitting Diode (LED)                                                                                                                                                                                                                                                                        | 79                                     |

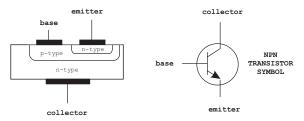

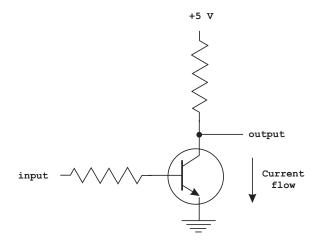

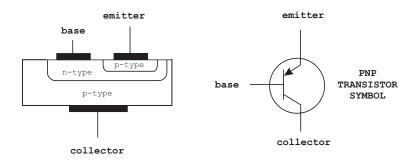

| 5.2  | 2 The Transistor<br>5.2.1 Bipolar Transistor                                                                                                                                                                                                                                                                | 81<br>81                               |

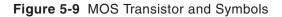

|      | 5.2.2 MOS Transistor                                                                                                                                                                                                                                                                                        | 83                                     |

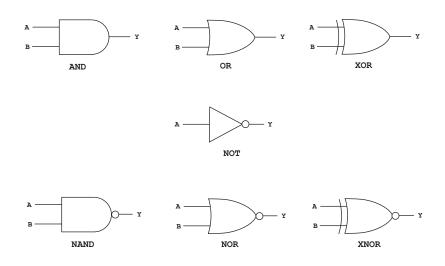

| 5.3  | B Logic Gates                                                                                                                                                                                                                                                                                               | 84                                     |

|      | Transistor-Transistor Logic                                                                                                                                                                                                                                                                                 | 85                                     |

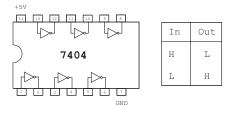

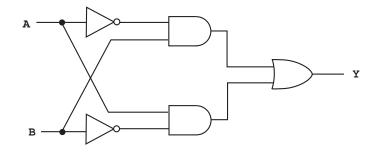

|      | 5.4.1 Inverter Gates                                                                                                                                                                                                                                                                                        | 86                                     |

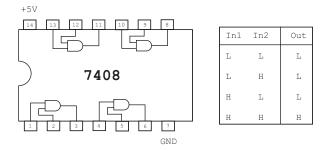

|      | 5.4.2 The AND Gate                                                                                                                                                                                                                                                                                          | 87                                     |

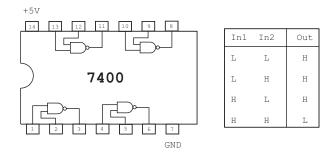

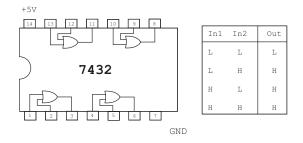

|      | 5.4.3 The NAND Gate<br>5.4.4 The OR Gate                                                                                                                                                                                                                                                                    | 87<br>88                               |

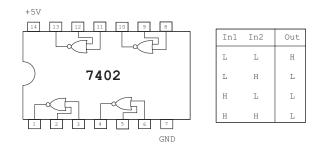

|      | 5.4.5 The NOR Gate                                                                                                                                                                                                                                                                                          | 88                                     |

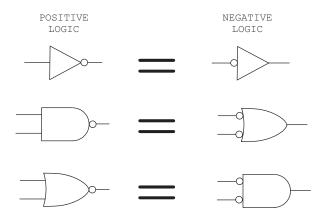

|      | 5.4.6 Positive and Negative Logic                                                                                                                                                                                                                                                                           | 89                                     |

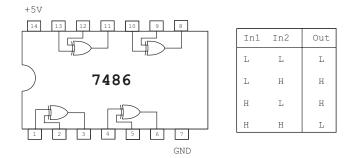

|      | 5.4.7 The XOR Gate                                                                                                                                                                                                                                                                                          | 90                                     |

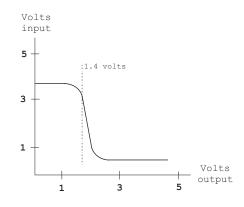

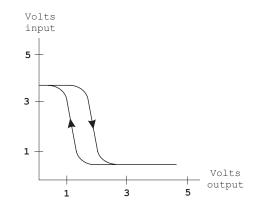

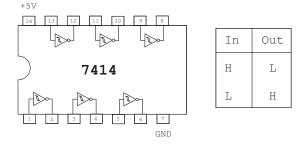

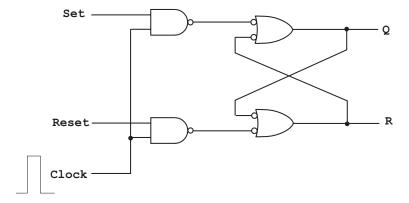

|      | 5.4.8 Schmitt Trigger Inverter                                                                                                                                                                                                                                                                              | 91                                     |

|      | Other TTL Logic Families                                                                                                                                                                                                                                                                                    | 93                                     |

| 5.6  | 6 CMOS Logic Gates                                                                                                                                                                                                                                                                                          | 93                                     |

| Chap | oter 6 - Circuit Components                                                                                                                                                                                                                                                                                 | 95                                     |

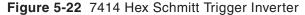

| 6.0  | Power Supplies                                                                                                                                                                                                                                                                                              | 95                                     |

| 6.1  | Clocked Logic and Flip-flops                                                                                                                                                                                                                                                                                | 96                                     |

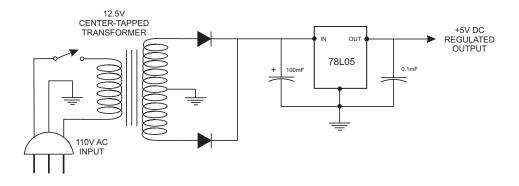

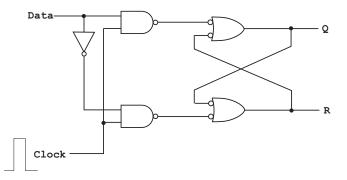

|      | 6.1.1 The RS Flip-flop                                                                                                                                                                                                                                                                                      | 96                                     |

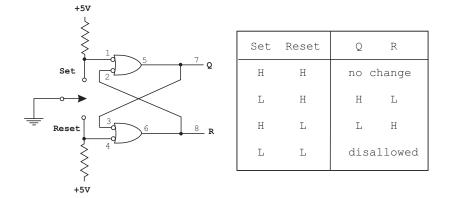

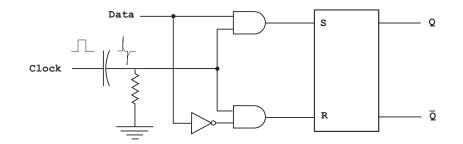

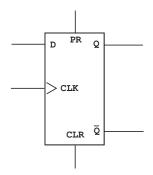

|      | 6.1.2 Clocked RS Flip-flop<br>6.1.3 The D Flip-flop                                                                                                                                                                                                                                                         | 98<br>99                               |

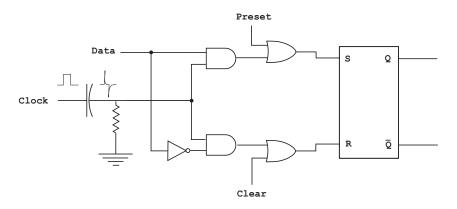

|      | 6.1.4 The Edge-triggered D Flip-flop                                                                                                                                                                                                                                                                        | 100                                    |

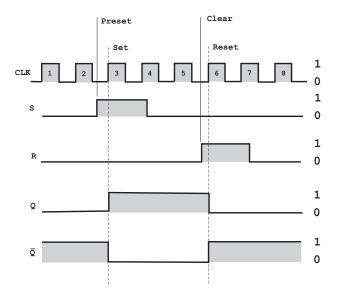

|      | 6.1.5 Preset and Clear Signals                                                                                                                                                                                                                                                                              | 101                                    |

|      | 6.1.6 D Flip-flop Waveform Action                                                                                                                                                                                                                                                                           | 102                                    |

|      | 6.1.7 Flip-flop Applications                                                                                                                                                                                                                                                                                | 103                                    |

| 6.2  | 2 Clocks                                                                                                                                                                                                                                                                                                    | 103                                    |

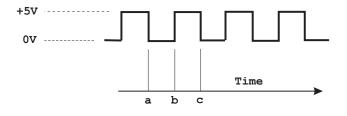

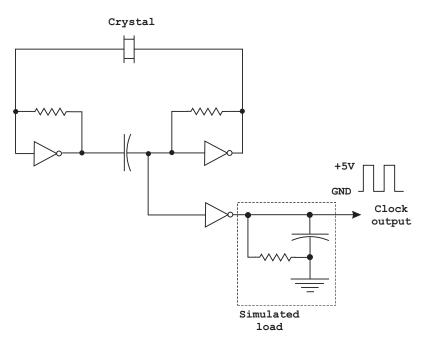

|      | 6.2.1 Clock Waveforms<br>6.2.2 The TTL Clock                                                                                                                                                                                                                                                                | 104<br>105                             |

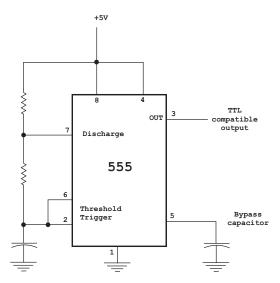

|      | 6.2.3 The 555 Timer                                                                                                                                                                                                                                                                                         | 105                                    |

|      |                                                                                                                                                                                                                                                                                                             |                                        |

|      | 6.2.4 Microcontroller Clocks                                | 106        |

|------|-------------------------------------------------------------|------------|

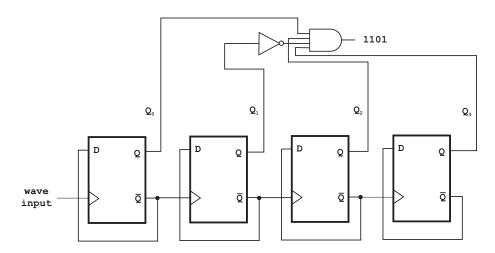

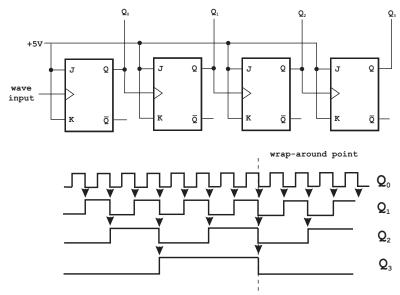

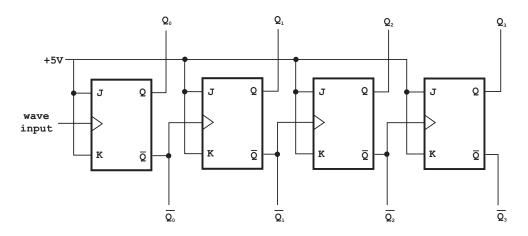

| 6.3  | Frequency Dividers and Counters                             | 107        |

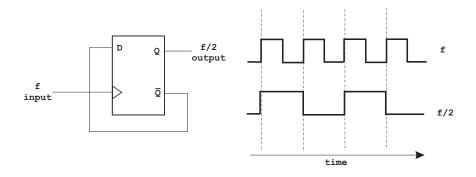

|      | 6.3.1 Frequency Dividers                                    | 107        |

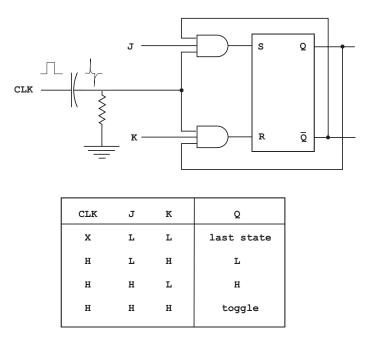

|      | 6.3.2 The JK Flip-flop Counter                              | 107        |

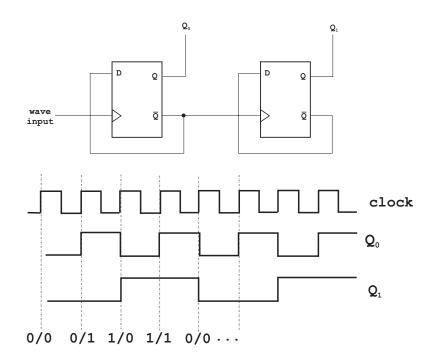

|      | 6.3.3 Ripple Counters                                       | 108        |

|      | 6.3.4 Decoding Gates                                        | 110        |

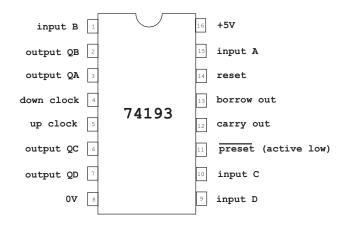

|      | 6.3.5 Synchronous Counters<br>6.3.6 Counter ICs             | 110<br>112 |

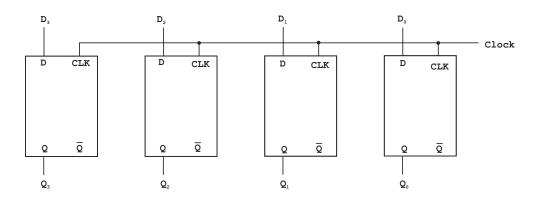

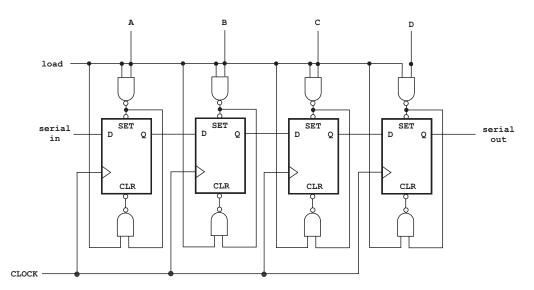

|      | 6.3.7 Shift Registers                                       | 112        |

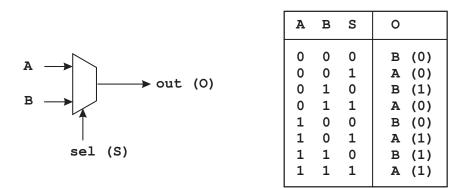

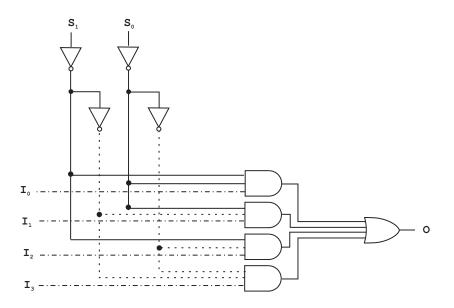

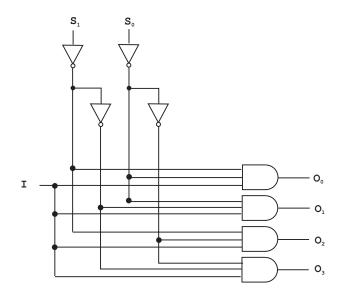

| 64   | Multiplexers and Demultiplexers                             | 115        |

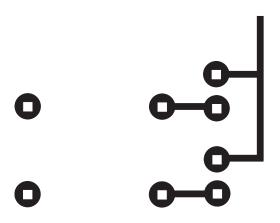

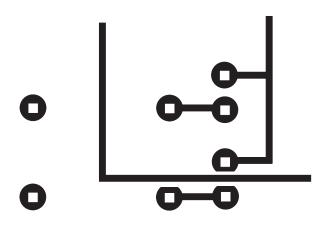

| 0.4  | 6.4.1 Multiplexers                                          | 115        |

|      | 6.4.2 Demultiplexers                                        | 118        |

|      | 6.4.3 Multiplexer and Demultiplexer ICs                     | 118        |

| 6.5  | Input Devices                                               | 118        |

|      | 6.5.1 Switches                                              | 118        |

|      | 6.5.2 Switch Contact Bounce                                 | 120        |

|      | 6.5.3 Keypads                                               | 121        |

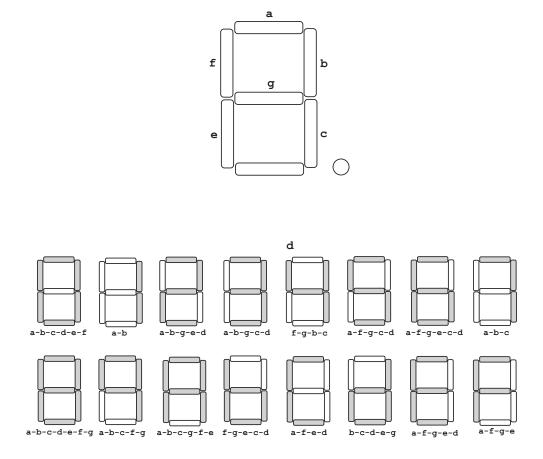

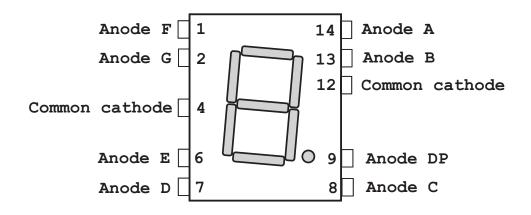

|      | 6.6 Output Devices                                          | 122        |

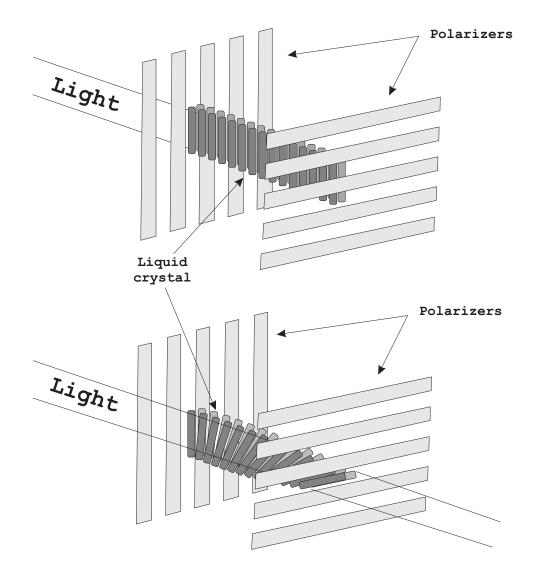

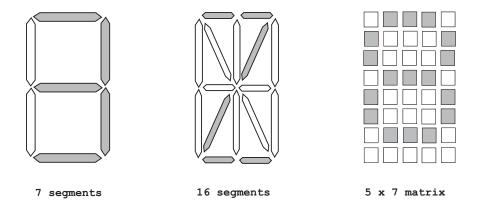

|      | 6.6.1 Seven-segment LED                                     | 122        |

|      | 6.6.2 Liquid Crystal Displays<br>6.6.3 LCD Technologies     | 124<br>125 |

|      | 6.6.3 LOD rechnologies                                      | 125        |

| Chap | ter 7 - The Microchip PIC                                   | 129        |

| •    | The PICMicro Microcontroller                                | 129        |

| 7.0  | 7.0.1 Programming the PIC                                   | 130        |

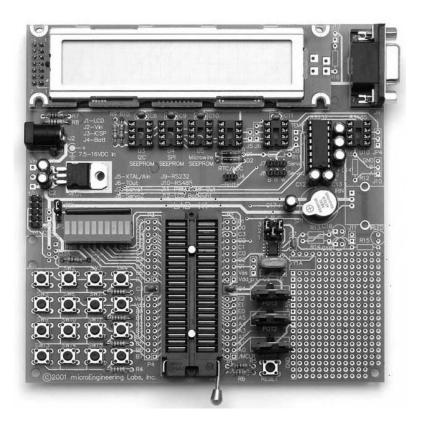

|      | PIC Programmers                                             | 131        |

|      | Development Boards                                          | 131        |

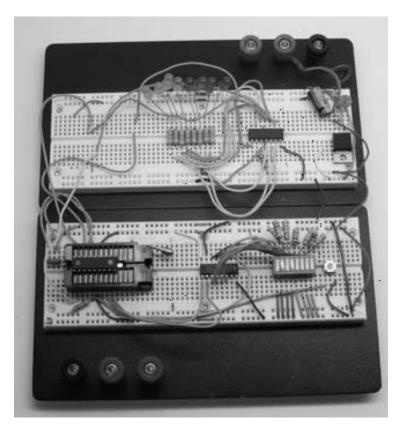

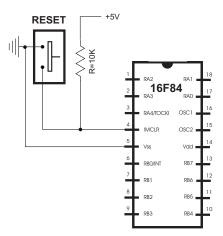

|      | 7.0.2 Prototyping the PIC Circuit                           | 132        |

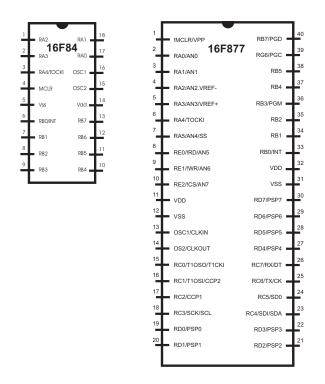

| 7.1  | PIC Architecture                                            | 134        |

|      | 7.1.1 Baseline PIC Family                                   | 134        |

|      | PIC10 Devices                                               | 135        |

|      | PIC12 Devices                                               | 135        |

|      | PIC14 Devices<br>7.1.2 Mid-range PIC Family                 | 138<br>138 |

|      | PIC16 Devices                                               | 130        |

|      | 7.1.3 High-Performance PIC Family                           | 139        |

|      | PIC18 Devices                                               | 139        |

|      |                                                             |            |

| Chap | ter 8 - Mid-range PIC Architecture                          | 141        |

| 8.0  | Processor Architecture and Design                           | 142        |

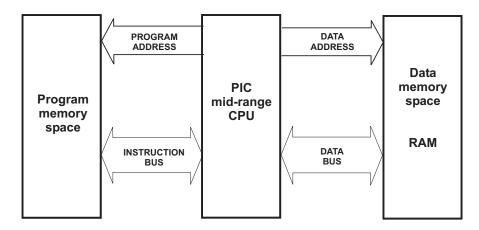

|      | 8.0.1 Harvard Architecture                                  | 142        |

|      | 8.0.2 RISC CPU Design                                       | 143        |

|      | 8.0.3 Single-word Instructions                              | 143        |

|      | 8.0.4 Instruction Format<br>8.0.5 Mid-Range Device Versions | 144<br>145 |

| 0 1  | •                                                           |            |

| 0.1  | The Mid-range Core Features<br>8.1.1 Oscillator             | 145<br>145 |

|      | 8.1.2 System Reset                                          | 145        |

|      | 8.1.3 Interrupts                                            | 148        |

8.2 Mid-Range CPU and Instruction Set

www.4electron.com

|      | 8.2.1 Mid-Range Instruction Set                                         | 149        |

|------|-------------------------------------------------------------------------|------------|

|      | 8.2.2 STATUS and OPTION Registers                                       | 151        |

| 8.3  | EEPROM Data Storage                                                     | 153        |

| 0.4  | 8.3.1 EEPROM in Mid-Range PICs                                          | 153        |

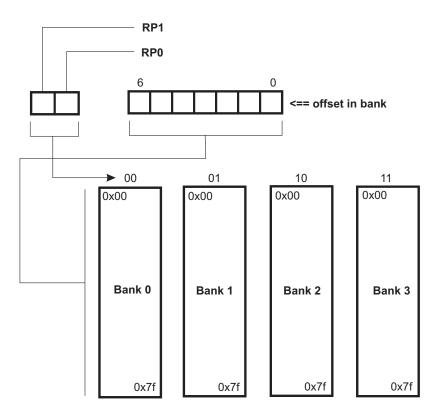

| 8.4  | Data Memory Organization                                                | 154        |

|      | <ul><li>8.4.1 The w Register</li><li>8.4.2 The Data Registers</li></ul> | 154<br>154 |

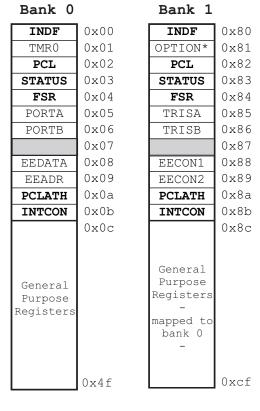

|      | Memory Banks                                                            | 154        |

|      | The SFRs                                                                | 155        |

|      | The GPRs                                                                | 157        |

|      | 8.4.3 Indirect Addressing                                               | 158        |

| 85   | Mid-range I/O and Peripheral Modules                                    | 158        |

| 0.0  | 8.5.1 I/O Ports                                                         | 159        |

|      | 8.5.2 Timer Modules                                                     | 160        |

|      | 8.5.3 Capture-and-Compare Module                                        | 160        |

|      | 8.5.4 Master Synchronous Serial Port (MSSP) Module                      | 161        |

|      | 8.5.5 USART Module                                                      | 161        |

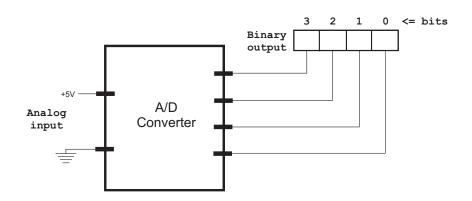

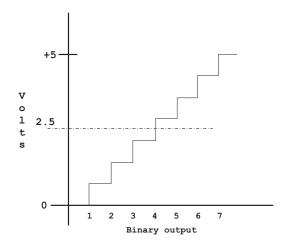

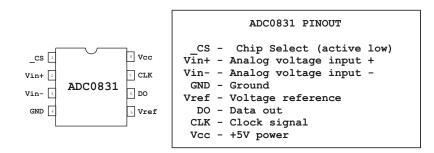

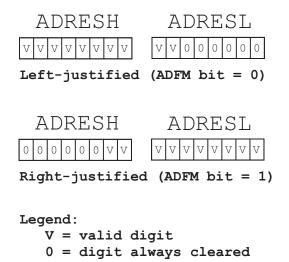

|      | 8.5.6 A/D Module                                                        | 161        |

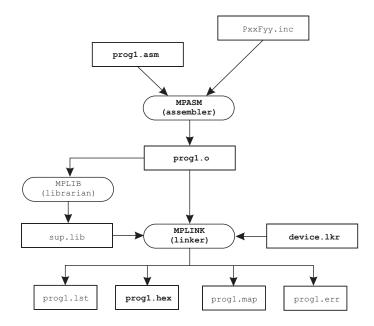

| Chap | ter 9 - PIC Programming: Tools and Techniques                           | 163        |

| -    |                                                                         | 163        |

| 9.0  | Microchip's MPLAB<br>9.0.1 Embedded Systems                             | 164        |

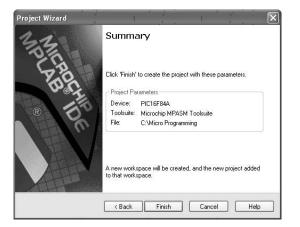

| 91   | Integrated Development Environment                                      | 165        |

| 0.1  | 9.1.1 Installing MPLAB                                                  | 165        |

|      | 9.1.2 Creating the Project                                              | 167        |

|      | 9.1.3 Project Build Options                                             | 169        |

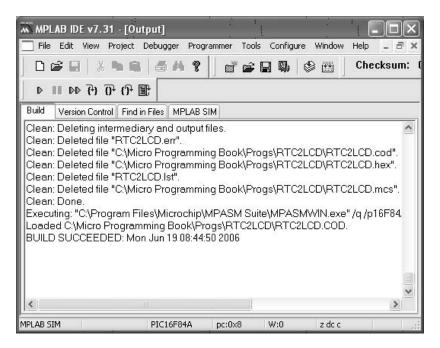

|      | 9.1.4 Building the Project                                              | 169        |

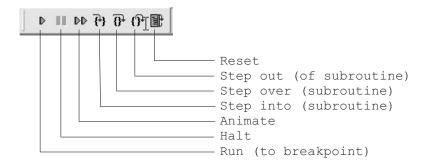

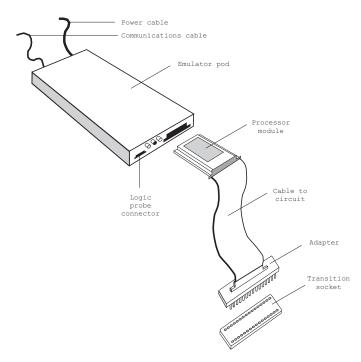

| 9.2  | Simulators and Debuggers                                                | 170        |

|      | 9.2.1 MPLAB SIM                                                         | 171        |

|      | 9.2.2 MPLAB Hardware Debuggers                                          | 172        |

|      | 9.2.3 A "Quick-and-Dirty" Debugger                                      | 174        |

| 9.3  | Programmers                                                             | 174        |

| 9.4  | Engineering PIC Software                                                | 175        |

|      | 9.4.1 Using Program Comments                                            | 176        |

|      | Program Header                                                          | 176        |

|      | Commented Banners                                                       | 177        |

|      | Commented Bitmaps                                                       | 178        |

|      | 9.4.2 Defining Data Elements                                            | 179        |

|      | The cblock Directive                                                    | 179        |

|      | 9.4.3 Banking Techniques<br>The banksel Directive                       | 180<br>180 |

|      | Bank Selection Macros                                                   | 180        |

|      | Deprecated Banking Instructions                                         | 180        |

|      | 9.4.4 Processor and Configuration Controls                              | 182        |

|      | Configuration Bits                                                      | 182        |

|      | 9.4.5 Naming Conventions                                                | 184        |

|      | 9.4.6 Errorlevel Directive                                              | 186        |

| 9.5  | Pseudo Instructions                                                     | 186        |

|      |                                                                         |            |

| Chapt | er 10 - Programming Essentials: Input and Output                          | 189        |

|-------|---------------------------------------------------------------------------|------------|

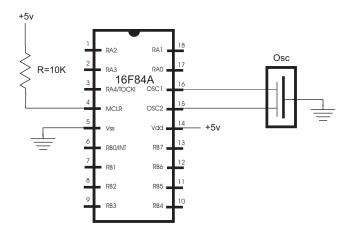

| 10.0  | 16F84A Programming Template                                               | 189        |

|       | Introducing the 16F84A                                                    | 191        |

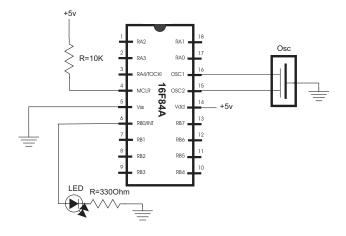

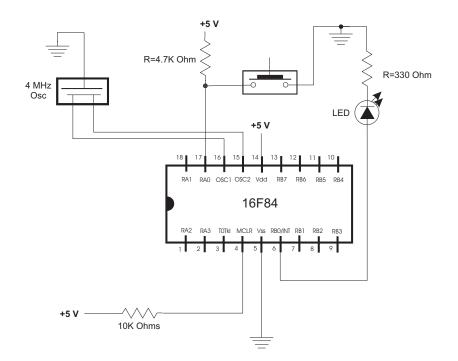

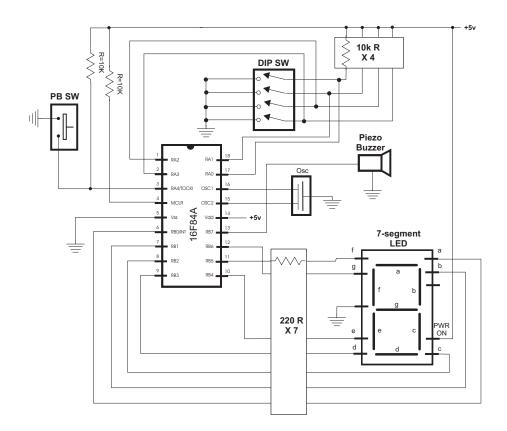

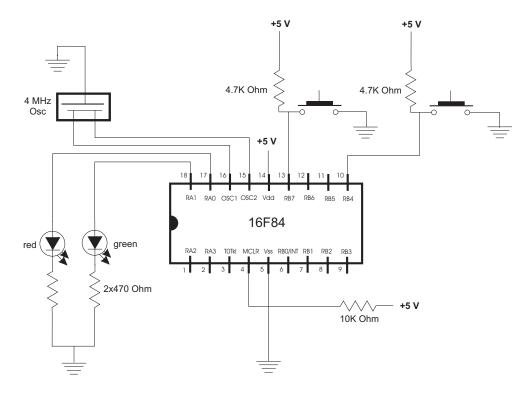

| -     | 10.1.1 Template Circuit for 16F84A                                        | 191        |

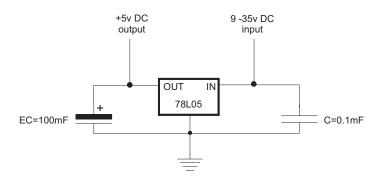

|       | 10.1.2 Power Supplies                                                     | 191        |

|       | Voltage Regulator                                                         | 192        |

|       | 10.1.3 Comparisons in PIC Programming<br>The Infamous PIC Carry Flag      | 193<br>194 |

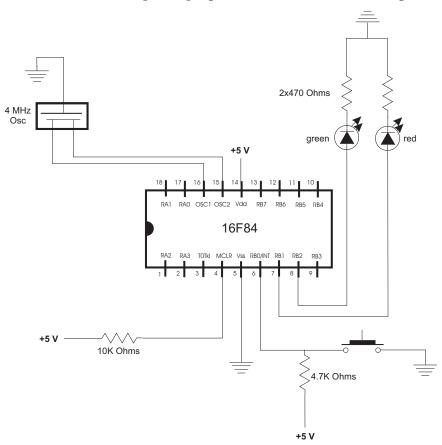

| 10.2  | Simple Circuits and Programs                                              | 194        |

| 10.2  | 10.2.1 A Single LED Circuit                                               | 194        |

|       | LED Flasher Program                                                       | 196        |

|       | 10.2.2 LED/Pushbutton Circuit                                             | 199        |

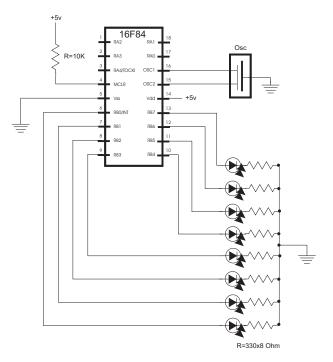

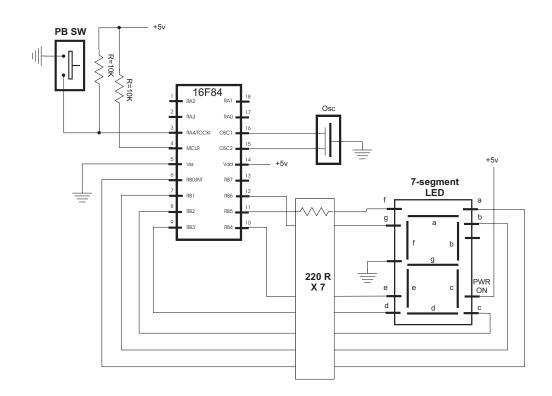

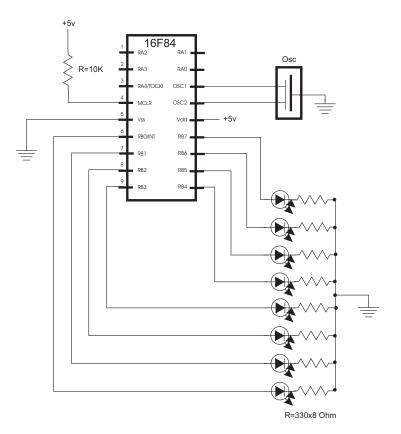

|       | 10.2.3 Multiple LED Circuit                                               | 202        |

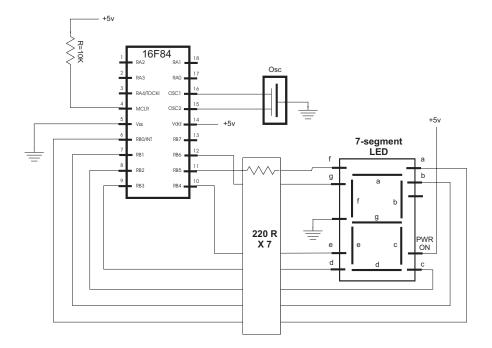

| 10.3  | Programming the Seven-segment LED                                         | 204        |

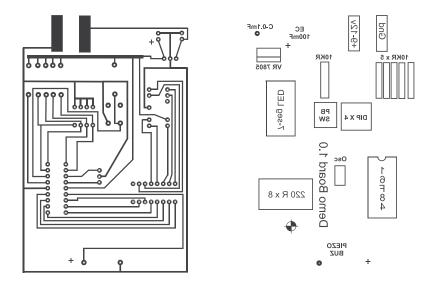

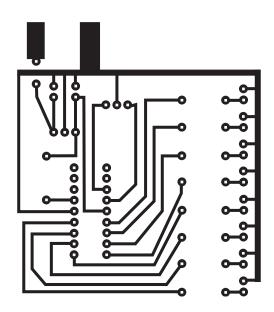

| 10.4  | A Demonstration Board                                                     | 206        |

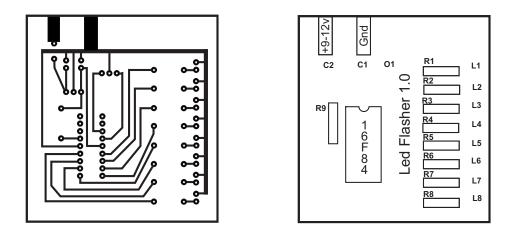

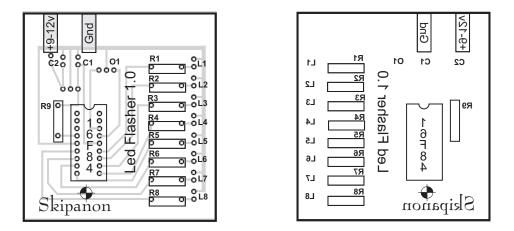

|       | 10.4.1 PCB Images for Demo Board                                          | 206        |

|       | 10.4.2 TestDemo1 Program                                                  | 208        |

| Chapt | er 11 - Interrupts                                                        | 211        |

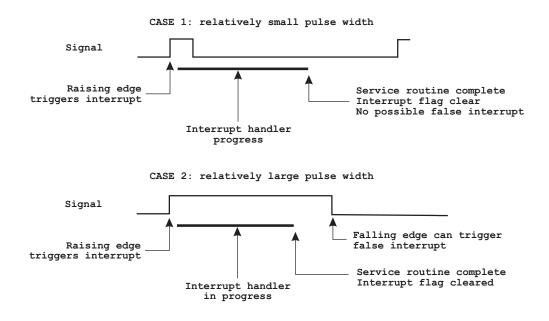

| 11.0  | Interrupts on the 16F84                                                   | 211        |

|       | 11.0.1 The Interrupt Control Register                                     | 211        |

|       | 11.0.2 The OPTION Register                                                | 212        |

| 11.1  | Interrupt Sources                                                         | 213        |

|       | 11.1.1 Port-B External Interrupt<br>11.1.2 Timer0 Interrupt               | 214<br>214 |

|       | 11.1.3 Port-B Line Change Interrupt                                       | 214        |

|       | Multiple External Interrupts                                              | 217        |

|       | 11.1.4 EEPROM Data Write Interrupt                                        | 217        |

| 11.2  | Interrupt Handlers                                                        | 217        |

|       | 11.2.1 Context Saving Operations                                          | 218        |

|       | Saving w and STATUS Registers                                             | 218        |

| 11.3  | Interrupt Programming                                                     | 218<br>219 |

|       | 11.3.1 Programming the External Interrupt<br>RB0 Interrupt Initialization | 219        |

|       | RB0 Interrupt Service Routine                                             | 221        |

|       | 11.3.2 Wakeup from SLEEP Using the RB0 Interrupt                          | 222        |

|       | The SleepDemo Program                                                     | 223        |

|       | 11.3.3 Port-B Bits 4-7 Status Change Interrupt                            | 224        |

|       | RB4-7 Interrupt Initialization<br>RB4-7 Change Interrupt Service Routine  | 225<br>227 |

| 11 /  | Sample Programs                                                           | 229        |

| 11.4  | 11.4.1 The RB0Int Program                                                 | 229        |

|       | 11.4.2 The SleepDemo Program                                              | 232        |

|       | 11.4.3 The RB4to7Int Program                                              | 235        |

| Chapt | er 12 - Timers and Counters                                               | 241        |

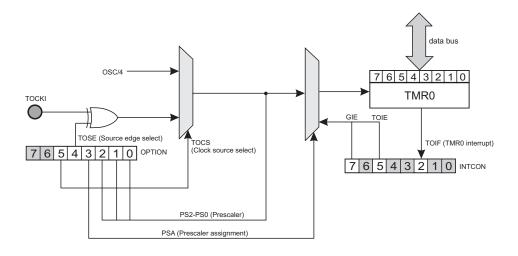

| •     | The 16F84 Timer0 Module                                                   | 241        |

|       | 12.0.1 Timer0 Operation                                                   | 241        |

|       | Timer0 Interrupt                                                    | 242        |

|-------|---------------------------------------------------------------------|------------|

|       | Timer0 Prescaler                                                    | 242        |

| 12.1  | Delays Using Timer0                                                 | 243        |

|       | 12.1.1 Long Delay Loops                                             | 244        |

|       | How Accurate the Delay?                                             | 245        |

|       | The Black-Ammerman Method                                           | 245        |

| 12.2  | Timer0 as a Counter                                                 | 246        |

| 12.3  | Timer0 Programming                                                  | 247        |

|       | 12.3.1 Programming a Counter                                        | 247        |

|       | A Timer/Counter Test Circuit                                        | 248        |

|       | The Tmr0Counter Program                                             | 248        |

|       | 12.3.2 Timer0 as a Simple Delay Timer<br>12.3.3 Measured Time Lapse | 250<br>252 |

|       | Interrupt-driven Timer                                              | 252        |

| 12/   | The Watchdog Timer                                                  | 259        |

| 12.4  | 12.4.1 Watchdog Timer Programming                                   | 260        |

| 12.5  | Sample Programs                                                     | 260        |

| 12.5  | 12.5.1 The Tmr0Counter program                                      | 260        |

|       | 12.5.2 The Timer0 Program                                           | 263        |

|       | 12.5.3 The LapseTimer Program                                       | 265        |

|       | 12.5.4 The LapseTmrInt Program                                      | 269        |

|       |                                                                     |            |

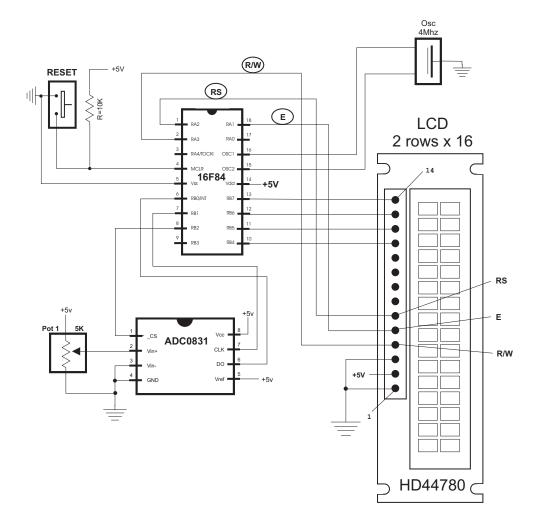

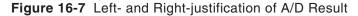

| Chapt | er 13 - LCD Interfacing and Programming                             | 275        |

| 13.0  | LCD Features and Architecture                                       | 275        |

|       | 13.0.1 LCD Functions and Components                                 | 276        |

|       | Internal Registers                                                  | 276        |

|       | Busy Flag                                                           | 276        |

|       | Address Counter                                                     | 276        |

|       | Display Data RAM (DDRAM)                                            | 276<br>276 |

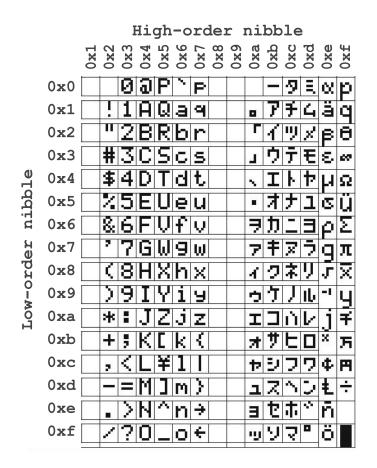

|       | Character Generator ROM (CGROM)<br>Character Generator RAM (CGRAM)  | 276        |

|       | Timing Generation Circuit                                           | 277        |

|       | Liquid Crystal Display Driver Circuit                               | 278        |

|       | Cursor/Blink Control Circuit                                        | 278        |

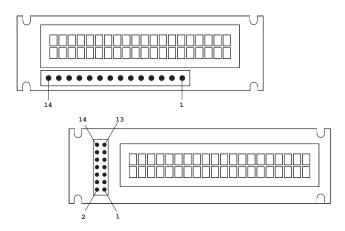

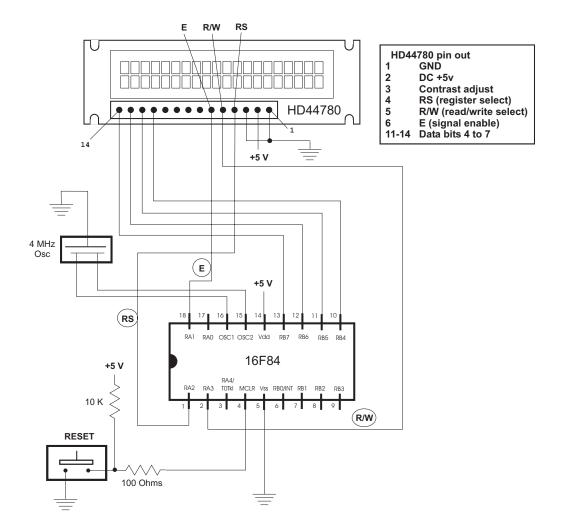

|       | 13.0.2 Connectivity and Pin-Out                                     | 278        |

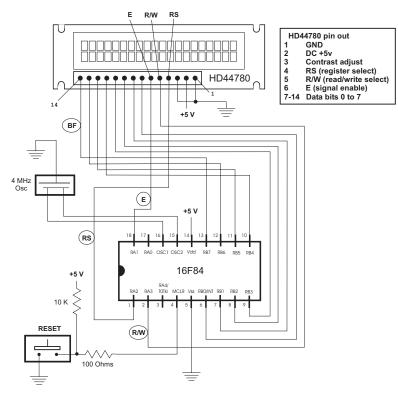

| 13.1  | Interfacing with the HD44780                                        | 279        |

|       | 13.1.1 Busy Flag or Timed Delay Options                             | 280        |

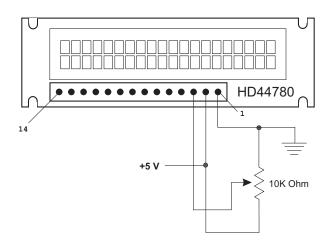

|       | 13.1.2 Contrast Control                                             | 281        |

|       | 13.1.3 Display Backlight                                            | 281        |

|       | 13.1.4 Display Memory Mapping                                       | 281        |

| 13.2  | HD44780 Instruction Set                                             | 283        |

|       | 13.2.1 Instruction Set Overview                                     | 283        |

|       | Clearing the Display                                                | 283        |

|       | Return home                                                         | 284        |

|       | Entry mode set<br>Display and Cursor ON/OFF                         | 284<br>284 |

|       | Cursor/display shift                                                | 284        |

|       | Function set                                                        | 285        |

|       | Set CGRAM address                                                   | 285        |

|       | Set DDRAM address                                                   | 285        |

|       | Read busy flag and Address register                                 | 285        |

|       | Write data                                                             | 285        |

|-------|------------------------------------------------------------------------|------------|

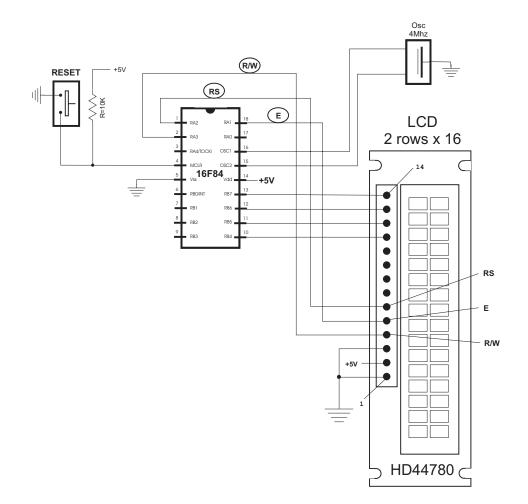

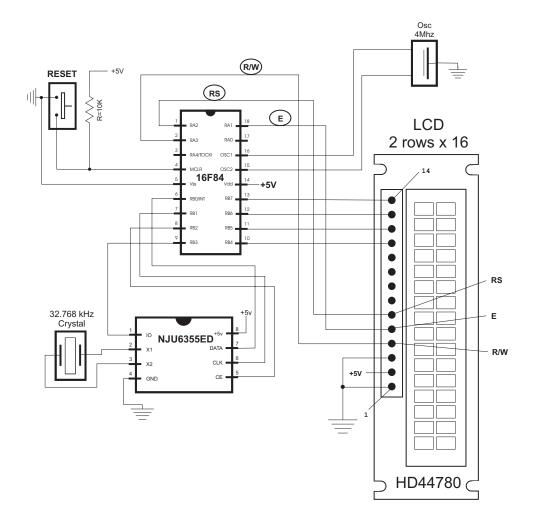

|       | Read data<br>13.2.2 A 16F84 8-bit Data Mode Circuit                    | 286        |

| 10.0  |                                                                        | 286        |

| 13.3  | LCD Programming                                                        | 287        |

|       | 13.3.1 Defining Constants and Variables<br>Using MPLAB Data Directives | 287<br>289 |

|       | 13.3.2 LCD Initialization                                              | 209        |

|       | Function Set Command                                                   | 290        |

|       | Display Off                                                            | 291        |

|       | Display and Cursor On                                                  | 291        |

|       | Set Entry Mode                                                         | 292        |

|       | Cursor and Display Shift                                               | 292        |

|       | Clear Display                                                          | 293        |

|       | 13.3.3 Auxiliary Operations                                            | 293        |

|       | Time Delay Routine<br>Pulsing the E Line                               | 293<br>295 |

|       | Reading the Busy Flag                                                  | 295        |

|       | Bit Merging Operations                                                 | 296        |

|       | 13.3.4 Text Data Storage and Display                                   | 298        |

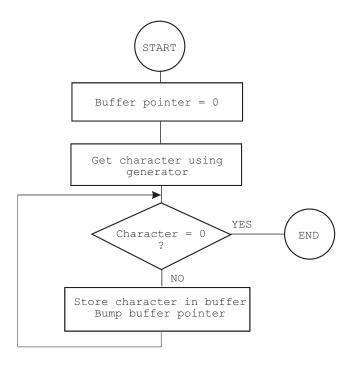

|       | Generating and Storing a Text String                                   | 299        |

|       | Displaying the Text String                                             | 301        |

|       | 13.3.5 Data Compression Techniques                                     | 302        |

|       | 4-bit Data Transfer Mode                                               | 302        |

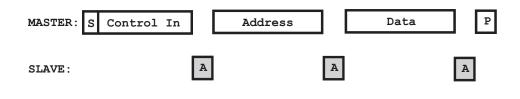

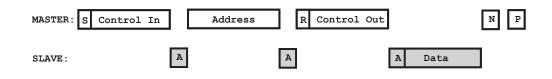

|       | Master/Slave Systems                                                   | 304        |

| 13.4  | Sample Programs                                                        | 306        |

|       | 13.4.1 LCDTest1                                                        | 306        |

|       | 13.4.2 LCDTest2 Program                                                | 316<br>327 |

|       | 13.4.3 LCDTest3 Program                                                | 527        |

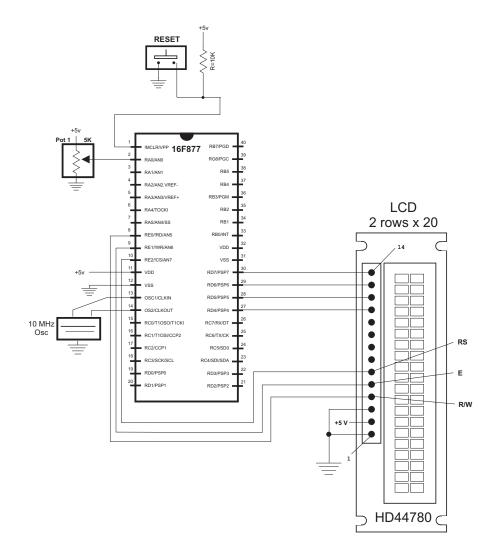

| Chapt | er 14 - Communications                                                 | 339        |

| 14.0  | PIC Communications Overview                                            | 339        |

| 14.1  | Serial Data Transmission                                               | 340        |

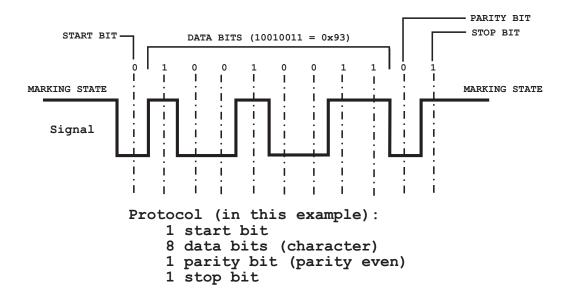

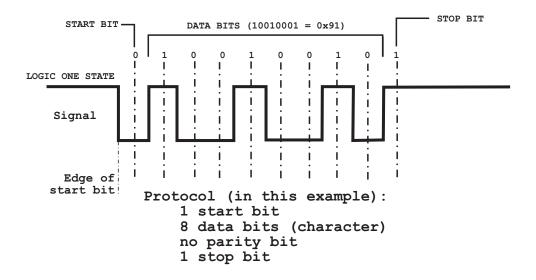

|       | 14.1.1 Asynchronous Serial Transmission                                | 340        |

|       | 14.1.2 Synchronous Serial Transmission                                 | 342        |

|       | 14.1.3 PIC Serial Communications                                       | 342        |

|       | 14.1.4 The RS-232-C Standard                                           | 343        |

|       | Essential Concepts<br>The Serial Bit Stream                            | 344<br>344 |

|       | Parity Testing                                                         | 344        |

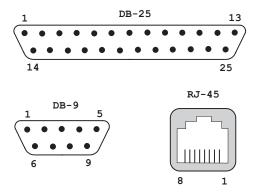

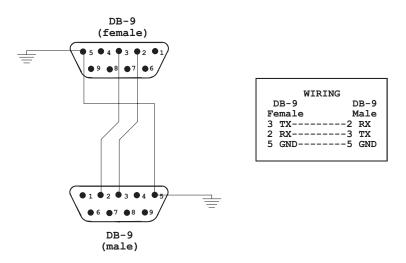

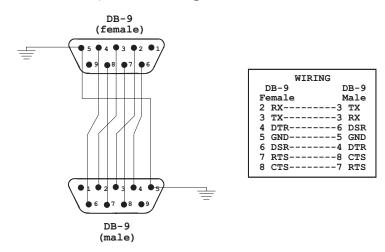

|       | Connectors and Wiring                                                  | 345        |

|       | The Null Modem                                                         | 346        |

|       | The Null Modem Cable                                                   | 347        |

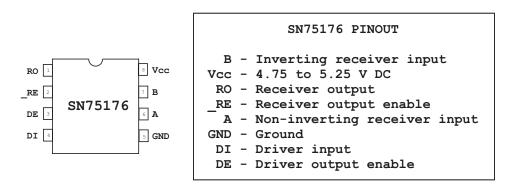

|       | 14.1.5 The EIA-485 Standard                                            | 349        |

|       | EIA-485 in PIC-based Systems                                           | 350        |

| 14.2  | Parallel Data Transmission                                             | 350        |

|       | 14.2.1 PIC Parallel Slave Port (PSP)                                   | 351        |

| 14.3  | PIC "Free-style" Serial Programming                                    | 351        |

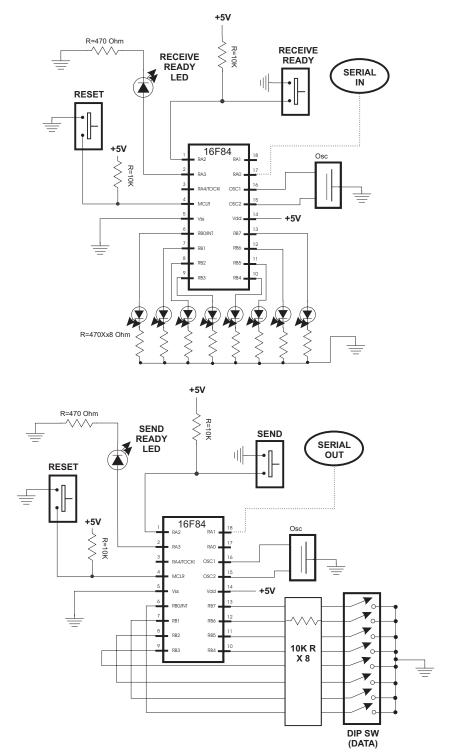

|       | 14.3.1 PIC-to-PIC Serial Communications                                | 352        |

|       | PIC-to-PIC Serial Communications Circuits                              | 352        |

|       | PIC-to-PIC Serial Communications Programs                              | 354        |

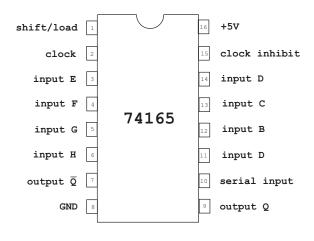

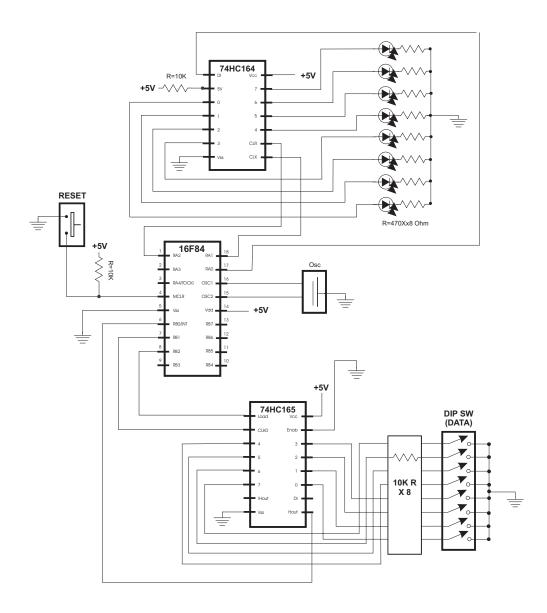

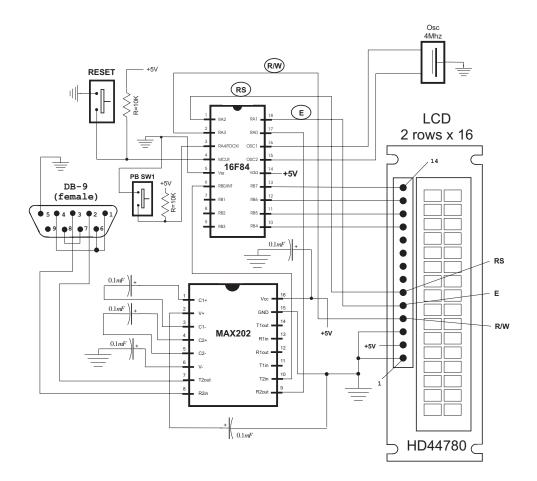

|       | 14.3.2 Program Using Shift Register ICs                                | 360        |

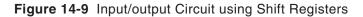

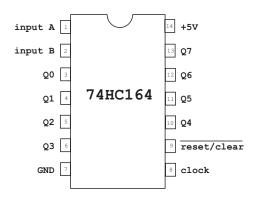

|       | The 74HC165 Parallel-to-Serial Shift Register<br>74HC164 Serial-to-Parallel Shift Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 361<br>364                                                                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 144   | PIC Protocol-based Serial Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 366                                                                                                                                                    |

| 17.7  | 14.4.1 RS-232-C Communications on the 16F84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 366                                                                                                                                                    |

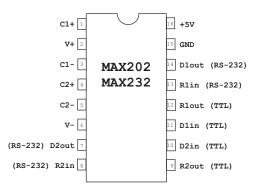

|       | The RS-232-C Transceiver IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 367                                                                                                                                                    |

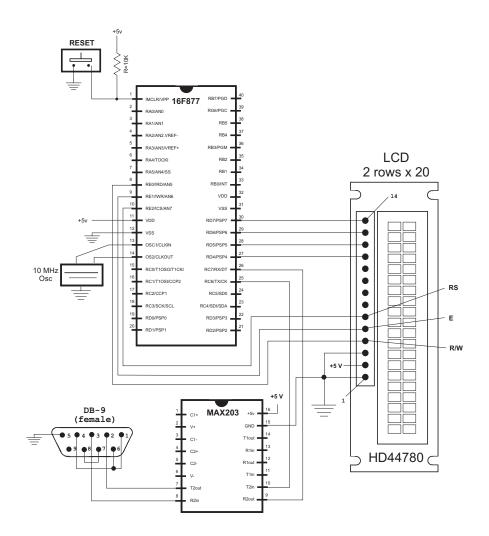

|       | PIC to PC Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 368                                                                                                                                                    |

|       | An RS-232-C TTY Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 368                                                                                                                                                    |

|       | A 16F84A UART Emulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 369                                                                                                                                                    |

|       | An LCD Scrolling Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 371                                                                                                                                                    |

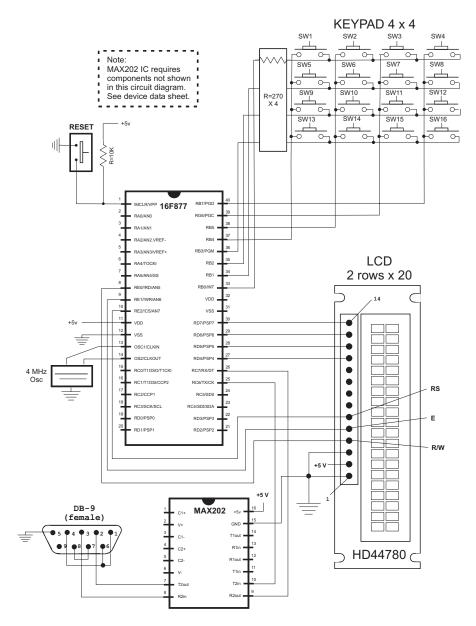

|       | 14.4.2 RS-232-C Communications on the 16F87x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 375                                                                                                                                                    |

|       | The 16F87x USART Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 376                                                                                                                                                    |

|       | The USART Baud Rate Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 376                                                                                                                                                    |

|       | 16F87x USART Asynchronous Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 379                                                                                                                                                    |

|       | 16F87x USART Asynchronous Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 380                                                                                                                                                    |

|       | PIC-to-PC RS-232-C Communications Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 381                                                                                                                                                    |

|       | 16F877 PIC Initialization Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 381                                                                                                                                                    |

|       | USART Receive and Transmit Routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 384                                                                                                                                                    |

|       | The USART Receive Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 386                                                                                                                                                    |

| 14.5  | Sample Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 389                                                                                                                                                    |

|       | 14.5.1 SerialSnd Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 389                                                                                                                                                    |

|       | 14.5.2 SerialRcv Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 394                                                                                                                                                    |

|       | 14.5.3 Serial6465 Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 400                                                                                                                                                    |

|       | 14.5.4 TTYUsart Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 404                                                                                                                                                    |

|       | 14.5.5 SerComLCD Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 420                                                                                                                                                    |

|       | 14.5.6 SerIntLCD Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 438                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

| Chapt | er 15 - Data EEPROM Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 459                                                                                                                                                    |

| -     | <b>- -</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>459</b><br>460                                                                                                                                      |

| -     | er 15 - Data EEPROM Programming<br>PIC Internal EEPROM Memory<br>15.0.1 EEPROM Programming on the 16F84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                        |