ESD in Silicon Integrated Circuits, 2nd Edition Ajith Amerasekera, Charvaka Duvvury Copyright © 2002 John Wiley & Sons, Ltd ISBNs: 0-471-49871-8 (Hardback); 0-470-84605-4 (Electronic)

## ESD in Silicon Integrated Circuits

Second Edition

# **ESD in Silicon Integrated Circuits**

#### Second Edition

#### Ajith Amerasekera Charvaka Duvvury

Texas Instruments, Inc., USA

#### With

#### **Warren Anderson**

Compaq Computer Corporation, USA

#### **Horst Gieser**

Fraunhofer Institute for Reliability and Microintegration IZM ATIS, Germany

#### **Sridhar Ramaswamy**

Texas Instruments, Inc., USA

Copyright © 2002 by John Wiley & Sons, Ltd., Baffins Lane, Chichester, West Sussex PO 19 1UD, England

Phone (+44) 1243 779777

e-mail (for orders and customer service enquiries): cs-books@wiley.co.uk

Visit our Home Page on http://www.wileyeurope.com or http://www.wiley.com

All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except under the terms of the Copyright, Designs and Patents Act 1988 or under the terms of a license issued by the Copyright Licensing Agency Ltd., 90 Tottenham Court Road, London W1P 0LP, UK without the permission in writing of the Publisher. Requests to the Publisher should be addressed to the Permissions Department, John Wiley & Sons, Ltd., Baffins Lane, Chichester, West Sussex PO 19 1UD, England, or emailed to permreq@wiley.co.uk, or faxed to (+44) 1243 770571.

Other Wiley Editorial Offices

John Wiley & Sons, Inc., 605 Third Avenue,

New York, NY 10158-0012, USA

Jossey-Bass, 989 Market Street, San Francisco, CA 94103-1741, USA

WILEY-VCH Verlag GmbH, Pappelallee 3, D-69469 Weinheim, Germany

John Wiley & Sons Australia, Ltd., 33 Park Road, Milton, Queensland 4064, Australia

John Wiley & Sons (Asia) Pte Ltd., 2 Clementi Loop #02-01, Jin Xing Distripark, Singapore 129809

John Wiley & Sons Canada, Ltd., 22 Worcester Road, Etobicoke, Ontario, Canada M9W 1L1

#### British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

ISBN 0 470 49871 8

Typeset in 10/12pt Times by Laserwords Private Limited, Chennai, India. Printed and bound in Great Britain by Antony Rowe Ltd., Chippenham, Wiltshire. This book is printed on acid-free paper responsibly manufactured from sustainable forestry in which at least two trees are planted for each one used for paper production.

## **Contents**

|   | Pref  | ace                                                   | ix |

|---|-------|-------------------------------------------------------|----|

| 1 | Intro | oduction                                              | 1  |

|   | 1.1   | Background                                            | 1  |

|   | 1.2   | The ESD Problem                                       | 3  |

|   | 1.3   | Protecting Against ESD                                | 4  |

|   | 1.4   | Outline of the Book                                   | 4  |

|   | 1.1   | Bibliography                                          | 7  |

| 2 | ESD   | Phenomenon                                            | 8  |

|   | 2.1   | Introduction                                          | 8  |

|   | 2.2   | Electrostatic Voltage                                 | 9  |

|   | 2.3   | Discharge                                             | 11 |

|   | 2.4   | ESD Stress Models                                     | 12 |

|   |       | Bibliography                                          | 15 |

| 3 | Test  | Methods                                               | 17 |

|   | 3.1   | Introduction                                          | 17 |

|   | 3.2   | Human Body Model (HBM)                                | 18 |

|   | 3.3   | Machine Model (MM)                                    | 27 |

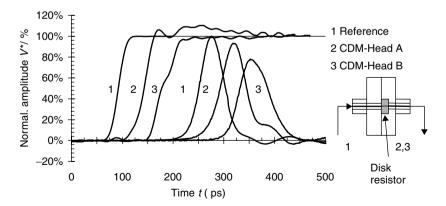

|   | 3.4   | Charged Device Model (CDM)                            | 28 |

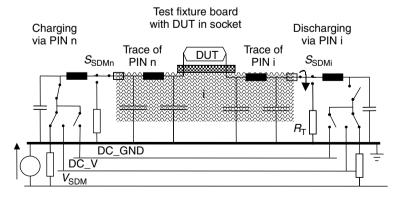

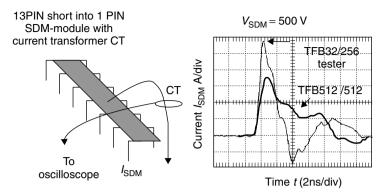

|   | 3.5   | Socket Device Model (SDM)                             | 40 |

|   | 3.6   | Metrology, Calibration, Verification                  | 42 |

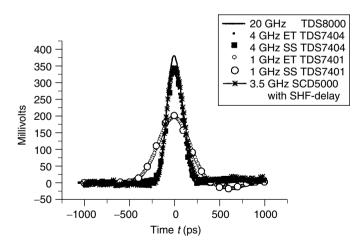

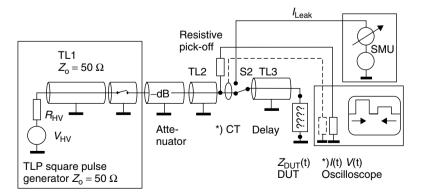

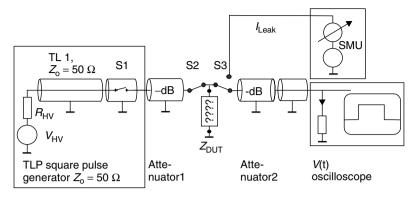

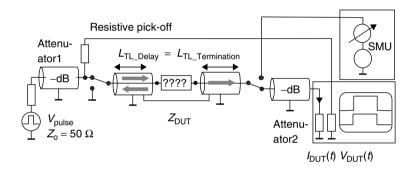

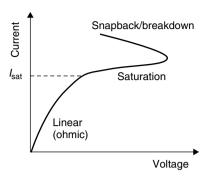

|   | 3.7   | Transmission Line Pulsing (TLP)                       | 47 |

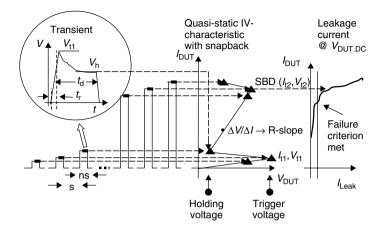

|   | 3.8   | Failure Criteria                                      | 58 |

|   | 3.9   | Summary                                               | 60 |

|   |       | Bibliography                                          | 61 |

| 4 | Phys  | sics and Operation of ESD Protection Circuit Elements | 68 |

|   | 4.1   | Introduction                                          | 68 |

|   | 4.2   | Resistors                                             | 68 |

|   | 43    | Diodes                                                | 70 |

| vi | CONTENTS |

|----|----------|

|    |          |

|   | 4.4  | Transistor Operation                            | 77  |

|---|------|-------------------------------------------------|-----|

|   | 4.5  | Transistor Operation under ESD Conditions       | 85  |

|   | 4.6  | Electrothermal Effects                          | 95  |

|   | 4.7  | SCR Operation                                   | 98  |

|   | 4.8  | Conclusion                                      | 101 |

|   |      | Bibliography                                    | 102 |

| 5 | ESD  | Protection Circuit Design Concepts and Strategy | 105 |

|   | 5.1  | The Qualities of Good ESD Protection            | 106 |

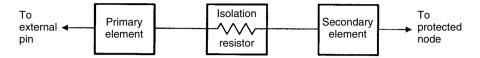

|   | 5.2  | ESD Protection Design Methods                   | 109 |

|   | 5.3  | Selecting an ESD Strategy                       | 123 |

|   | 5.4  | Summary                                         | 124 |

|   |      | Bibliography                                    | 124 |

| 6 | Desi | gn and Layout Requirements                      | 126 |

|   | 6.1  | Introduction                                    | 126 |

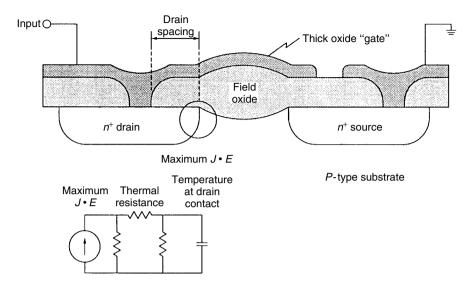

|   | 6.2  | Thick Field Device                              | 127 |

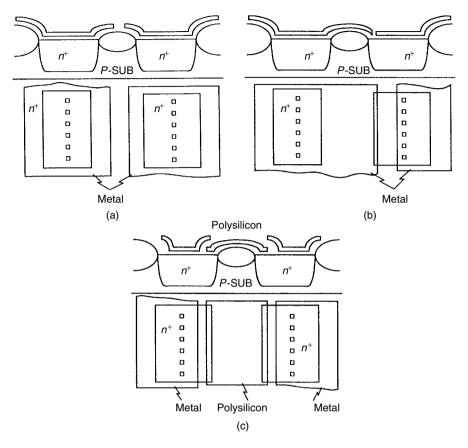

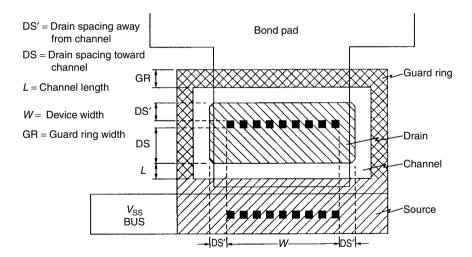

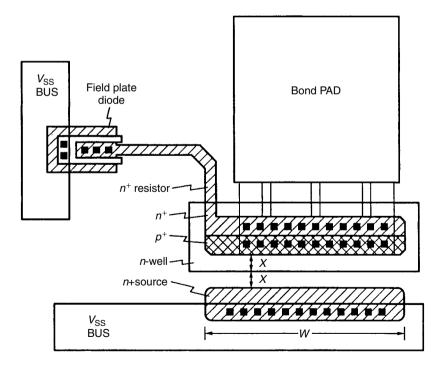

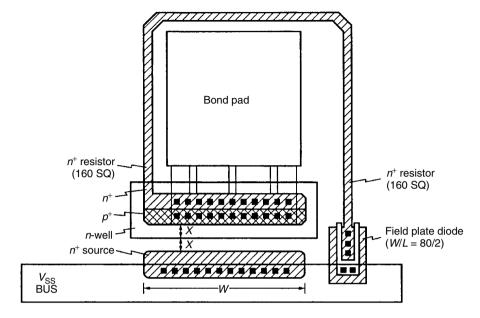

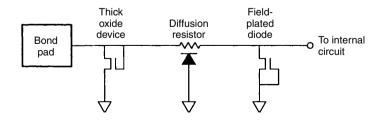

|   | 6.3  | nMOS Transistors (FPDs)                         | 132 |

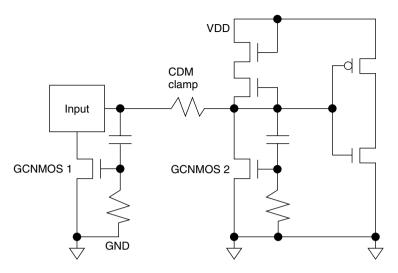

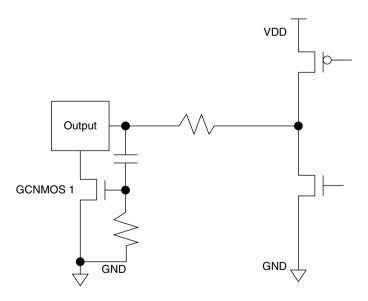

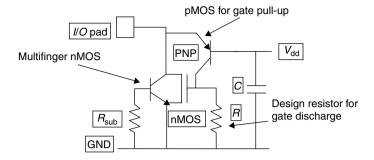

|   | 6.4  | Gate-Coupled nMOS (GCNMOS)                      | 138 |

|   | 6.5  | Gate Driven nMOS (GDNMOS)                       | 149 |

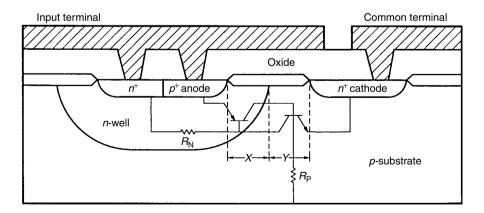

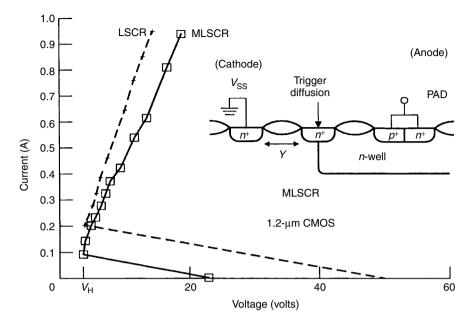

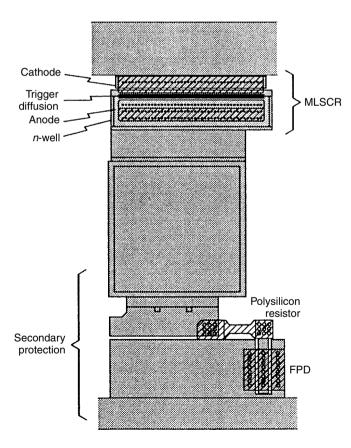

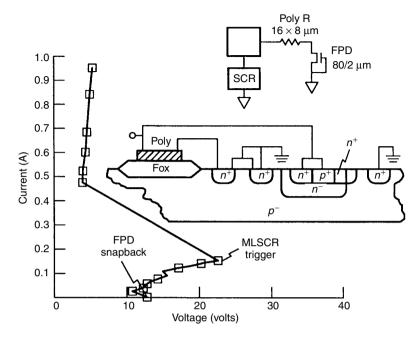

|   | 6.6  | SCR Protection Device                           | 150 |

|   | 6.7  | ESD Protection Design Synthesis                 | 155 |

|   | 6.8  | Total Input Protection                          | 164 |

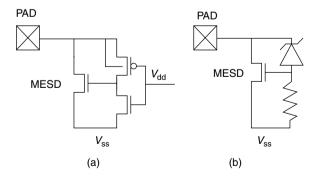

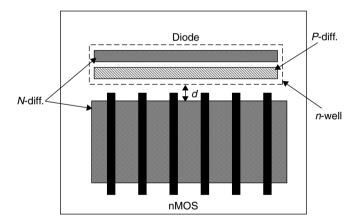

|   | 6.9  | ESD Protection Using Diode-Based Devices        | 172 |

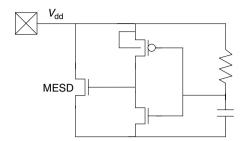

|   | 6.10 | Power Supply Clamps                             | 176 |

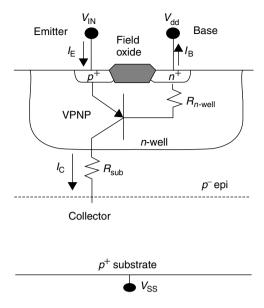

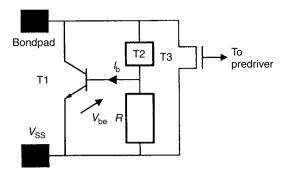

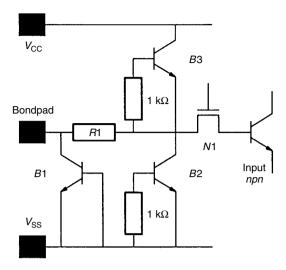

|   | 6.11 | Bipolar and BiCMOS Protection Circuits          | 179 |

|   | 6.12 | Summary                                         | 183 |

|   |      | Bibliography                                    | 184 |

| 7 | Adva | anced Protection Design                         | 188 |

|   | 7.1  | Introduction                                    | 188 |

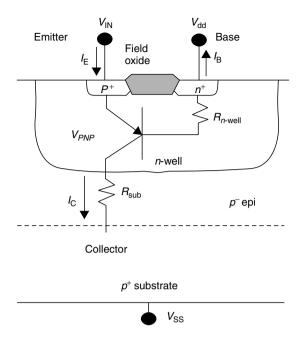

|   | 7.2  | PNP-Driven nMOS (PDNMOS)                        | 188 |

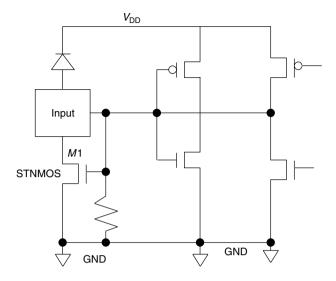

|   | 7.3  | Substrate Triggered nMOS (STNMOS)               | 189 |

|   | 7.4  | nMOS Triggered nMOS (NTNMOS)                    | 192 |

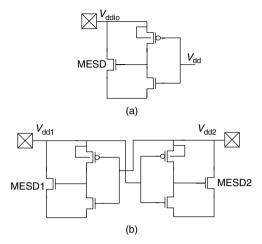

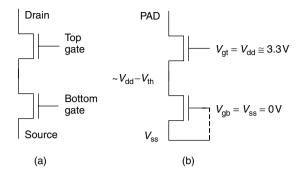

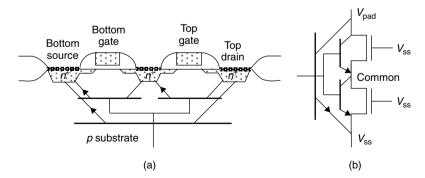

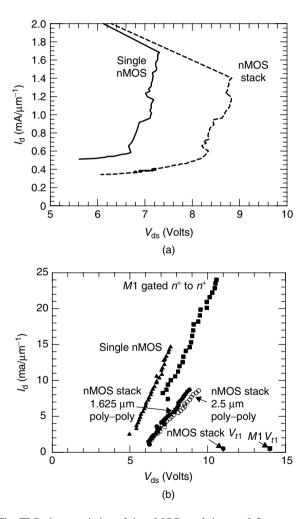

|   | 7.5  | ESD for Mixed-Voltage I/O                       | 200 |

|   | 7.6  | CDM Protection                                  | 214 |

|   | 7.7  | SOI Technology                                  | 215 |

|   | 7.8  | High-Voltage Transistors                        | 216 |

|   | 7.9  | BiCMOS Protection                               | 218 |

|   | 7.10 | RF Designs                                      | 219 |

|   |      | General I/O Protection Schemes                  | 220 |

|   | 7.12 | Design/Layout Errors                            | 221 |

|   |      | Summary                                         | 223 |

|   |      | Bibliography                                    | 224 |

|   |      |                                                 |     |

| CONTENTS | vii |

|----------|-----|

|          |     |

| 8.1 Introduction       228         8.2 Failure Mode Analysis       229         8.3 Reliability and Performance Considerations       238         8.4 Advanced CMOS Input Protection       239         8.5 Optimizing the Input Protection Scheme       242         8.6 Designs for Special Applications       249         8.7 Process Effects on Input Protection Design       253         8.8 Total IC Chip Protection       255         8.9 Power Bus Protection       256         8.10 Internal Chip ESD Damage       258         8.11 Stress Dependent ESD Behavior       263         8.12 Failure Mode Case Studies       267         8.13 Summary       271         Bibliography       272         9 Influence of Processing on ESD       282         9.1 Introduction       282         9.2 High Current Behavior       284         9.3 Cross Section of a MOS Transistor       287         9.4 Drain-Source Implant Effects       288         9.5 p-Well Effects       293         9.6 n-Well Effects       293         9.7 Epitaxial Layers and Substrates       295         9.8 Gate Oxides       298         9.9 Silicides       300         9.11 Interconnect and Metalization       305     < | 8  | Failu | re Modes, Reliability Issues, and Case Studies | 228 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|------------------------------------------------|-----|

| 8.2       Failure Mode Analysis       229         8.3       Reliability and Performance Considerations       238         8.4       Advanced CMOS Input Protection       239         8.5       Optimizing the Input Protection Scheme       242         8.6       Designs for Special Applications       249         8.7       Process Effects on Input Protection Design       253         8.8       Total IC Chip Protection       255         8.9       Power Bus Protection       256         8.10       Internal Chip ESD Damage       258         8.11       Stress Dependent ESD Behavior       263         8.12       Failure Mode Case Studies       267         8.13       Summary       271         Bibliography       272         9       Influence of Processing on ESD       282         9.1       Introduction       282         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       294         9.7       Epitaxial Layers and Substrates       295                                         |    |       | •                                              |     |

| 8.3       Reliability and Performance Considerations       238         8.4       Advanced CMOS Input Protection       239         8.5       Optimizing the Input Protection Scheme       242         8.6       Designs for Special Applications       249         8.7       Process Effects on Input Protection Design       253         8.8       Total IC Chip Protection       255         8.9       Power Bus Protection       256         8.10       Internal Chip ESD Damage       258         8.11       Stress Dependent ESD Behavior       263         8.12       Failure Mode Case Studies       267         8.13       Summary       271         Bibliography       272         9       Influence of Processing on ESD       282         9.1       Introduction       282         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       294         9.7       Epitaxial Layers and Substrates       295         9.8       Gate Oxides       300                                                   |    |       |                                                |     |

| 8.4       Advanced CMOS Input Protection       239         8.5       Optimizing the Input Protection Scheme       242         8.6       Designs for Special Applications       249         8.7       Process Effects on Input Protection Design       253         8.8       Total IC Chip Protection       255         8.9       Power Bus Protection       256         8.10       Internal Chip ESD Damage       258         8.11       Stress Dependent ESD Behavior       263         8.12       Failure Mode Case Studies       267         8.13       Summary       271         Bibliography       272         9       Influence of Processing on ESD       282         9.1       Introduction       282         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       294         9.7       Epitaxial Layers and Substrates       295         9.9       Silicides       300         9.10       Contacts       304         9.11                                                                         |    |       | · · · · · · · · · · · · · · · · · · ·          |     |

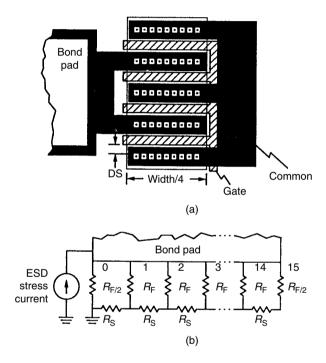

| 8.5       Optimizing the Input Protection Scheme       242         8.6       Designs for Special Applications       249         8.7       Process Effects on Input Protection       253         8.8       Total IC Chip Protection       256         8.9       Power Bus Protection       256         8.10       Internal Chip ESD Damage       258         8.11       Stress Dependent ESD Behavior       263         8.12       Failure Mode Case Studies       267         8.13       Summary       271         Bibliography       272         9       Influence of Processing on ESD       282         9.1       Introduction       282         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       293         9.7       Epitaxial Layers and Substrates       295         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       306         9.12       Ga                                                                       |    |       | •                                              |     |

| 8.6       Designs for Special Applications       249         8.7       Process Effects on Input Protection Design       253         8.8       Total IC Chip Protection       255         8.9       Power Bus Protection       256         8.10       Internal Chip ESD Damage       258         8.11       Stress Dependent ESD Behavior       263         8.12       Failure Mode Case Studies       267         8.13       Summary       271         Bibliography       272         9       Influence of Processing on ESD       282         9.1       Introduction       282         9.2       High Current Behavior       284         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       293         9.7       Epitaxial Layers and Substrates       295         9.8       Gate Oxides       298         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization </td <td></td> <td></td> <td>*</td> <td></td>                           |    |       | *                                              |     |

| 8.7       Process Effects on Input Protection Design       253         8.8       Total IC Chip Protection       255         8.9       Power Bus Protection       256         8.10       Internal Chip ESD Damage       258         8.11       Stress Dependent ESD Behavior       263         8.12       Failure Mode Case Studies       267         8.13       Summary       271         Bibliography       272         9       Introduction       282         9.1       Introduction       282         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       294         9.7       Epitaxial Layers and Substrates       295         9.9       Silicides       300         9.10       Contacts       300         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.14       Bipolar Transistors                                                                                   |    |       | 1 0 1                                          |     |

| 8.8       Total IC Chip Protection       255         8.9       Power Bus Protection       256         8.10       Internal Chip ESD Damage       258         8.11       Stress Dependent ESD Behavior       263         8.12       Failure Mode Case Studies       267         8.13       Summary       271         Bibliography       272         9       Influence of Processing on ESD       282         9.1       Introduction       282         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       293         9.7       Epitaxial Layers and Substrates       295         9.8       Gate Oxides       298         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.15       Diodes       314                                                                                                   |    |       | • • •                                          |     |

| 8.9       Power Bus Protection       256         8.10       Internal Chip ESD Damage       258         8.11       Stress Dependent ESD Behavior       263         8.12       Failure Mode Case Studies       267         8.13       Summary       271         Bibliography       272         9       Influence of Processing on ESD       282         9.1       Introduction       282         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       293         9.7       Epitaxial Layers and Substrates       295         9.8       Gate Oxides       298         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.14       Bipolar Transistors       312         9.15       Diodes       314 <tr< td=""><td></td><td></td><td></td><td>255</td></tr<>                                              |    |       |                                                | 255 |

| 8.11 Stress Dependent ESD Behavior       263         8.12 Failure Mode Case Studies       267         8.13 Summary       271         Bibliography       272         9 Influence of Processing on ESD       282         9.1 Introduction       282         9.2 High Current Behavior       284         9.3 Cross Section of a MOS Transistor       287         9.4 Drain-Source Implant Effects       288         9.5 p-Well Effects       293         9.6 n-Well Effects       294         9.7 Epitaxial Layers and Substrates       295         9.9 Silicides       300         9.10 Contacts       304         9.11 Interconnect and Metalization       305         9.12 Gate Length Dependencies       306         9.13 Silicon-on-Insulator (SOI)       310         9.14 Bipolar Transistors       312         9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                    |    |       |                                                | 256 |

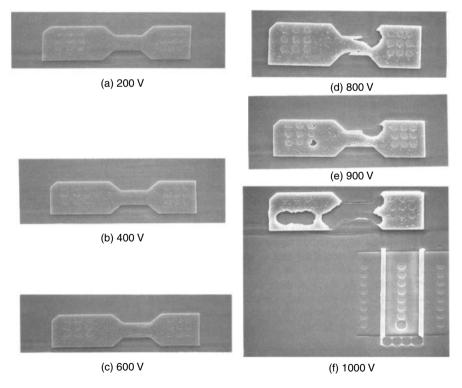

| 8.11 Stress Dependent ESD Behavior       263         8.12 Failure Mode Case Studies       267         8.13 Summary       271         Bibliography       272         9 Influence of Processing on ESD       282         9.1 Introduction       282         9.2 High Current Behavior       284         9.3 Cross Section of a MOS Transistor       287         9.4 Drain-Source Implant Effects       288         9.5 p-Well Effects       293         9.6 n-Well Effects       294         9.7 Epitaxial Layers and Substrates       295         9.9 Silicides       300         9.10 Contacts       304         9.11 Interconnect and Metalization       305         9.12 Gate Length Dependencies       306         9.13 Silicon-on-Insulator (SOI)       310         9.14 Bipolar Transistors       312         9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                    |    | 8.10  | Internal Chip ESD Damage                       | 258 |

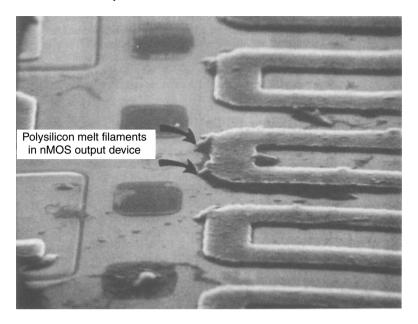

| 8.12 Failure Mode Case Studies       267         8.13 Summary       271         Bibliography       272         9 Influence of Processing on ESD       282         9.1 Introduction       282         9.2 High Current Behavior       284         9.3 Cross Section of a MOS Transistor       287         9.4 Drain-Source Implant Effects       288         9.5 p-Well Effects       293         9.6 n-Well Effects       294         9.7 Epitaxial Layers and Substrates       295         9.8 Gate Oxides       298         9.9 Silicides       300         9.10 Contacts       304         9.11 Interconnect and Metalization       305         9.12 Gate Length Dependencies       306         9.13 Silicon-on-Insulator (SOI)       310         9.14 Bipolar Transistors       312         9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                                       |    |       |                                                | 263 |

| Bibliography       272         9 Influence of Processing on ESD       282         9.1 Introduction       282         9.2 High Current Behavior       284         9.3 Cross Section of a MOS Transistor       287         9.4 Drain-Source Implant Effects       288         9.5 p-Well Effects       293         9.6 n-Well Effects       294         9.7 Epitaxial Layers and Substrates       295         9.8 Gate Oxides       298         9.9 Silicides       300         9.10 Contacts       304         9.11 Interconnect and Metalization       305         9.12 Gate Length Dependencies       306         9.13 Silicon-on-Insulator (SOI)       310         9.14 Bipolar Transistors       312         9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                                                                                                                       |    |       |                                                | 267 |

| 9 Influence of Processing on ESD       282         9.1 Introduction       282         9.2 High Current Behavior       284         9.3 Cross Section of a MOS Transistor       287         9.4 Drain-Source Implant Effects       288         9.5 p-Well Effects       293         9.6 n-Well Effects       294         9.7 Epitaxial Layers and Substrates       295         9.8 Gate Oxides       298         9.9 Silicides       300         9.10 Contacts       304         9.11 Interconnect and Metalization       305         9.12 Gate Length Dependencies       306         9.13 Silicon-on-Insulator (SOI)       310         9.14 Bipolar Transistors       312         9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                                                                                                                                                      |    | 8.13  | Summary                                        | 271 |

| 9.1       Introduction       282         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       294         9.7       Epitaxial Layers and Substrates       295         9.8       Gate Oxides       298         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.14       Bipolar Transistors       312         9.15       Diodes       314         9.16       Resistors       315         9.17       Reliability Trade-Offs       316         9.18       Summary       317         Bibliography       320         10       Device Modeling of High Current Effects       326         10.1       Introduction       326                                                                                                                                                                                 |    |       | Bibliography                                   | 272 |

| 9.1       Introduction       282         9.2       High Current Behavior       284         9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       294         9.7       Epitaxial Layers and Substrates       295         9.8       Gate Oxides       298         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.14       Bipolar Transistors       312         9.15       Diodes       314         9.16       Resistors       315         9.17       Reliability Trade-Offs       316         9.18       Summary       317         Bibliography       320         10       Device Modeling of High Current Effects       326         10.1       Introduction       326                                                                                                                                                                                 | 9  | Influ | ence of Processing on ESD                      | 282 |

| 9.2 High Current Behavior       284         9.3 Cross Section of a MOS Transistor       287         9.4 Drain-Source Implant Effects       288         9.5 p-Well Effects       293         9.6 n-Well Effects       294         9.7 Epitaxial Layers and Substrates       295         9.8 Gate Oxides       298         9.9 Silicides       300         9.10 Contacts       304         9.11 Interconnect and Metalization       305         9.12 Gate Length Dependencies       306         9.13 Silicon-on-Insulator (SOI)       310         9.14 Bipolar Transistors       312         9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                                                                                                                                                                                                                                            |    |       |                                                | 282 |

| 9.3       Cross Section of a MOS Transistor       287         9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       294         9.7       Epitaxial Layers and Substrates       295         9.8       Gate Oxides       298         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.14       Bipolar Transistors       312         9.15       Diodes       314         9.16       Resistors       315         9.17       Reliability Trade-Offs       316         9.18       Summary       317         Bibliography       320         10       Device Modeling of High Current Effects       326         10.1       Introduction       326                                                                                                                                                                                                                                                                            |    | -     |                                                |     |

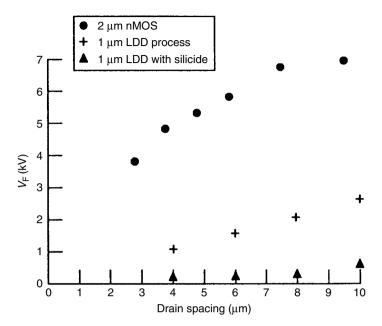

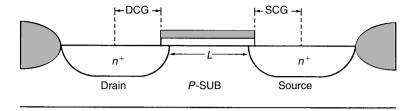

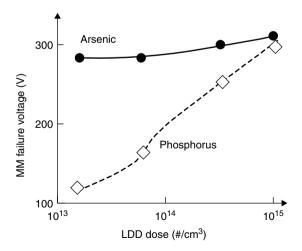

| 9.4       Drain-Source Implant Effects       288         9.5       p-Well Effects       293         9.6       n-Well Effects       294         9.7       Epitaxial Layers and Substrates       295         9.8       Gate Oxides       298         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.14       Bipolar Transistors       312         9.15       Diodes       314         9.16       Resistors       315         9.17       Reliability Trade-Offs       316         9.18       Summary       317         Bibliography       320         10       Device Modeling of High Current Effects       326         10.1       Introduction       326                                                                                                                                                                                                                                                                                                                                          |    |       | e                                              |     |

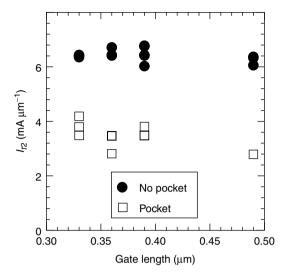

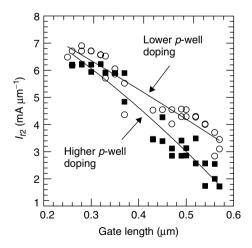

| 9.5 p-Well Effects  9.6 n-Well Effects  9.7 Epitaxial Layers and Substrates  9.8 Gate Oxides  9.9 Silicides  9.10 Contacts  9.11 Interconnect and Metalization  9.12 Gate Length Dependencies  9.13 Silicon-on-Insulator (SOI)  9.14 Bipolar Transistors  9.15 Diodes  9.16 Resistors  9.17 Reliability Trade-Offs  9.18 Summary  Bibliography  10 Device Modeling of High Current Effects  10.1 Introduction  293  294  294  294  294  294  294  295  295                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |                                                |     |

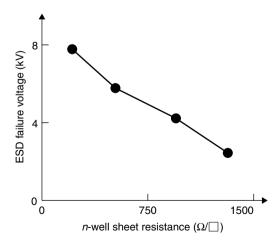

| 9.6 n-Well Effects 294 9.7 Epitaxial Layers and Substrates 295 9.8 Gate Oxides 298 9.9 Silicides 300 9.10 Contacts 304 9.11 Interconnect and Metalization 305 9.12 Gate Length Dependencies 306 9.13 Silicon-on-Insulator (SOI) 310 9.14 Bipolar Transistors 312 9.15 Diodes 314 9.16 Resistors 315 9.17 Reliability Trade-Offs 9.18 Summary Bibliography 317 Bibliography 320 10 Device Modeling of High Current Effects 326 10.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |       | ±                                              |     |

| 9.7       Epitaxial Layers and Substrates       295         9.8       Gate Oxides       298         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.14       Bipolar Transistors       312         9.15       Diodes       314         9.16       Resistors       315         9.17       Reliability Trade-Offs       316         9.18       Summary       317         Bibliography       320         10       Device Modeling of High Current Effects       326         10.1       Introduction       326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | •                                              |     |

| 9.8       Gate Oxides       298         9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.14       Bipolar Transistors       312         9.15       Diodes       314         9.16       Resistors       315         9.17       Reliability Trade-Offs       316         9.18       Summary       317         Bibliography       320         10       Device Modeling of High Current Effects       326         10.1       Introduction       326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 9.7   | Epitaxial Layers and Substrates                | 295 |

| 9.9       Silicides       300         9.10       Contacts       304         9.11       Interconnect and Metalization       305         9.12       Gate Length Dependencies       306         9.13       Silicon-on-Insulator (SOI)       310         9.14       Bipolar Transistors       312         9.15       Diodes       314         9.16       Resistors       315         9.17       Reliability Trade-Offs       316         9.18       Summary       317         Bibliography       320         10       Device Modeling of High Current Effects       326         10.1       Introduction       326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       | ÷                                              | 298 |

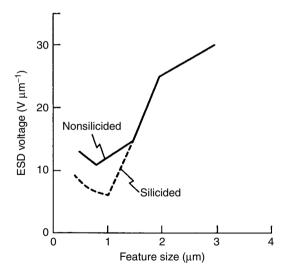

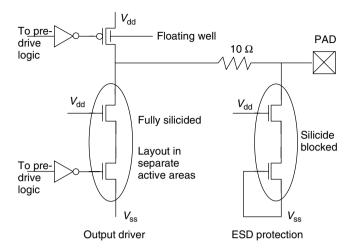

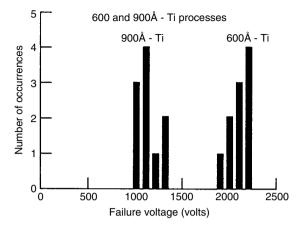

| 9.11 Interconnect and Metalization 9.12 Gate Length Dependencies 306 9.13 Silicon-on-Insulator (SOI) 9.14 Bipolar Transistors 9.15 Diodes 9.16 Resistors 9.17 Reliability Trade-Offs 9.18 Summary Bibliography 317 Bibliography 320  10 Device Modeling of High Current Effects 326 10.1 Introduction 305 316 317 317 326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 9.9   | Silicides                                      | 300 |

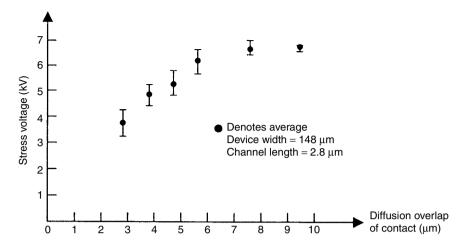

| 9.12 Gate Length Dependencies       306         9.13 Silicon-on-Insulator (SOI)       310         9.14 Bipolar Transistors       312         9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 9.10  | Contacts                                       | 304 |

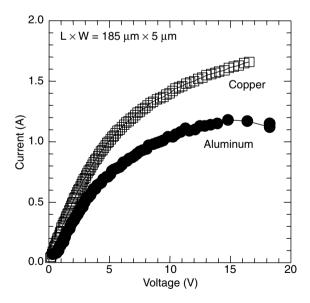

| 9.13 Silicon-on-Insulator (SOI)       310         9.14 Bipolar Transistors       312         9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 9.11  | Interconnect and Metalization                  | 305 |

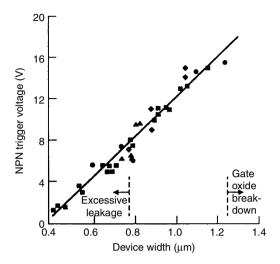

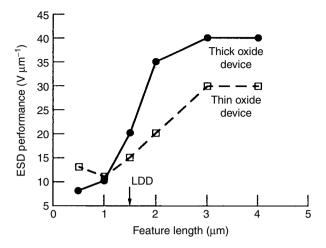

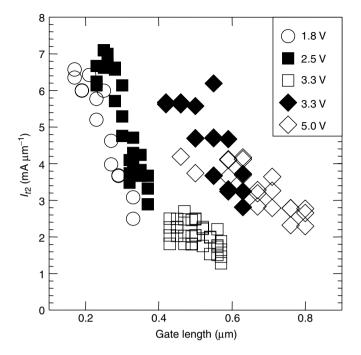

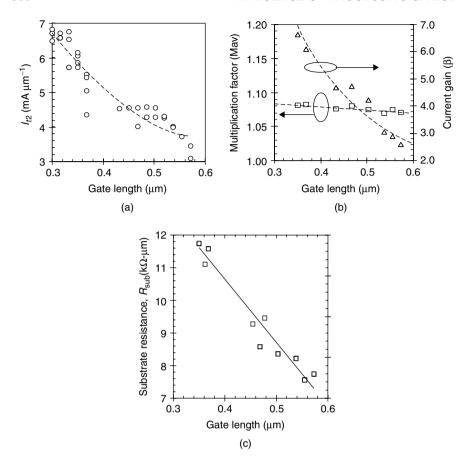

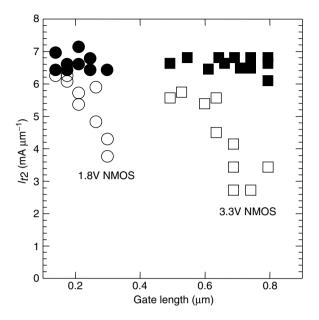

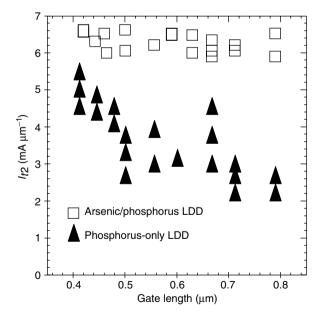

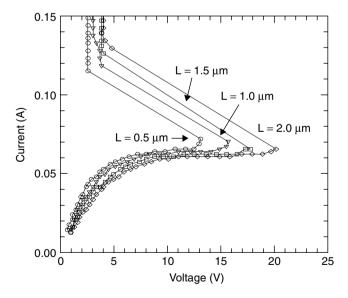

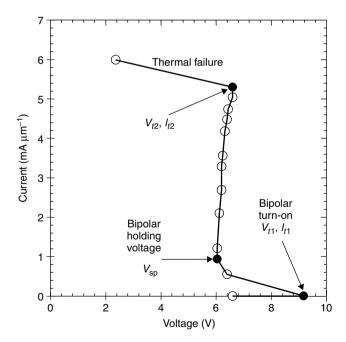

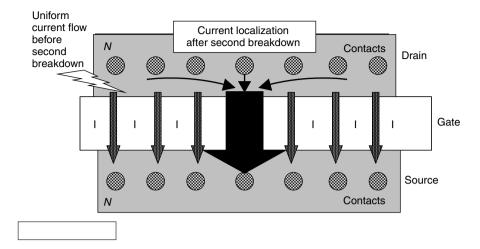

| 9.14 Bipolar Transistors       312         9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 9.12  | Gate Length Dependencies                       | 306 |

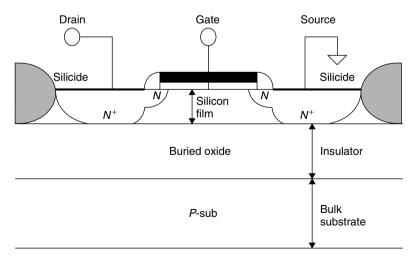

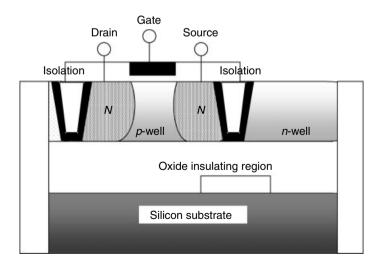

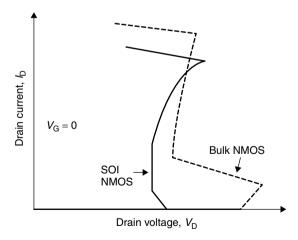

| 9.15 Diodes       314         9.16 Resistors       315         9.17 Reliability Trade-Offs       316         9.18 Summary       317         Bibliography       320         10 Device Modeling of High Current Effects       326         10.1 Introduction       326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 9.13  | Silicon-on-Insulator (SOI)                     | 310 |

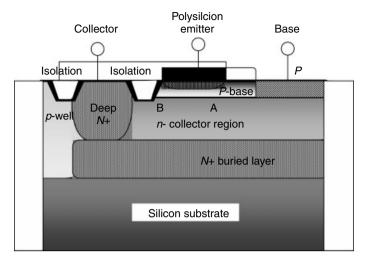

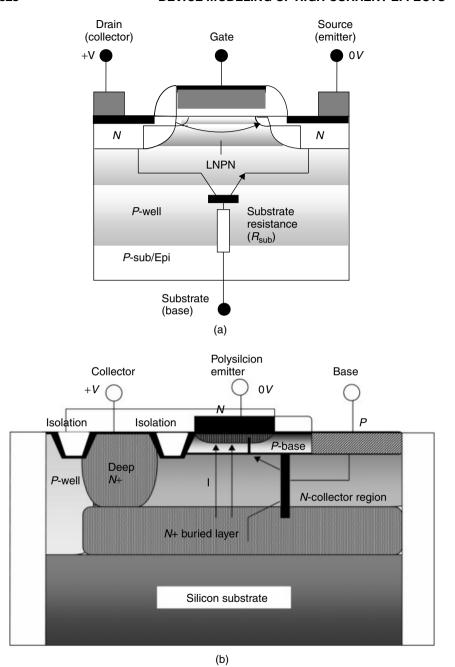

| 9.16 Resistors 9.17 Reliability Trade-Offs 9.18 Summary Bibliography 310 Device Modeling of High Current Effects 10.1 Introduction 326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 9.14  | Bipolar Transistors                            | 312 |

| 9.17 Reliability Trade-Offs 9.18 Summary Bibliography 317 Bibliography 320  10 Device Modeling of High Current Effects 326 10.1 Introduction 326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 9.15  | Diodes                                         | 314 |

| 9.18 Summary Bibliography 317 Bibliography 320  10 Device Modeling of High Current Effects 10.1 Introduction 326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 9.16  | Resistors                                      | 315 |

| Bibliography 320  10 Device Modeling of High Current Effects 326  10.1 Introduction 326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 9.17  | Reliability Trade-Offs                         | 316 |

| 10 Device Modeling of High Current Effects 326 10.1 Introduction 326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 9.18  | Summary                                        | 317 |

| 10.1 Introduction 326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |       | Bibliography                                   | 320 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 | Devi  | ce Modeling of High Current Effects            | 326 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 10.1  | Introduction                                   | 326 |

| 10.2 The Hysics of ESD Damage 327                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | The Physics of ESD Damage                      | 327 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |       | · · · · · · · · · · · · · · · · · · ·          | 330 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |       |                                                | 335 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |       | • •                                            | 339 |

| viii | i                                                       | CONTENTS |

|------|---------------------------------------------------------|----------|

|      | 10.6 Conclusion                                         | 344      |

|      | Bibliography                                            | 345      |

| 11   | Circuit Simulation Basics, Approaches, and Applications | 350      |

|      | 11.1 Introduction                                       | 350      |

|      | 11.2 Modeling the MOSFET                                | 351      |

|      | 11.3 Modeling Bipolar Junction Transistors              | 367      |

|      | 11.4 Modeling Diffusion Resistors                       | 371      |

|      | 11.5 Modeling Protection Diodes                         | 375      |

|      | 11.6 Simulation of Protection Circuits                  | 376      |

|      | 11.7 Electrothermal Circuit Simulations                 | 382      |

|      | 11.8 Conclusion                                         | 385      |

|      | Bibliography                                            | 389      |

| 12   | Conclusion                                              | 394      |

|      | 12.1 Long-Term Relevance of ESD In ICs                  | 394      |

|      | 12.2 State-of-the-Art for ESD Protection                | 395      |

|      | 12.3 Current Limitations                                | 396      |

|      | 12.4 Future Issues                                      | 398      |

|      | Bibliography                                            | 399      |

|      | Index                                                   | 401      |

### **Preface**

In the seven years since the first edition of this book was completed, Electrostatic Discharge (ESD) phenomena in integrated circuits (IC) continues to be important as technologies shrink and the speed and size of the chips increases. The phenomena related to ESD events in semiconductor devices take place outside the realm of normal device operation. Hence, the physics governing this behavior are not typically found in general textbooks on semiconductors. Similarly the circuit design issues involve nonstandard approaches that are not covered in general books on electronic design. There has been a large amount of work done in the areas of ESD circuit design and the physics involved, most of which has been published in a number of papers and conference proceedings. This book covers the state-of-the-art in circuit design for ESD prevention as well as the device physics, test methods, and characterization. We also include case studies showing examples of approaches to solving ESD design problems.

For the second edition, we have completely revised a number of chapters and brought other chapters up to date with the latest learning. The last seven years have seen many developments in the understanding of ESD phenomenon and the issues related to circuit and transistor design, as well as to modeling and simulation.

The book is intended for those working in the field of IC circuit design and transistor device design. In addition, the basics presented in this book should also appeal to graduate students in the field of semiconductor reliability and device/circuit modeling. As the problems associated with ESD become significant in the IC industry the demand for graduates with a basic knowledge of ESD phenomena also increases. We hope that this book will help students meet the demands of the IC industry in terms of understanding and approaching ESD problems in semiconductor devices.

There are many companies and research institutes that have made it possible to understand and solve the majority of ESD problems in ICs. Some of the companies that have been particularly active in recent years are Texas Instruments, Philips Semiconductors, Lucent, Rockwell, IBM, Motorola, DEC/Compaq, David Sarnoff Labs, and Intel. Research Institutes that have made significant contributions in recent years are Sandia National Labs, Clemson University, Stanford University, the University of California in Berkeley, the University of Western Ontario in Canada, the University of Illinois at Urbana-Champain, Twente University in The Netherlands, the Technical University of Munich and the Fraunhofer Institute both in Germany, and IMEC in Belgium.

We have many people to thank for their contributions to our personal knowledge and understanding in this area. We would particularly like to thank Robert Rountree, x PREFACE

Thomas Polgreen, and Amitava Chatterjee for their contributions both at the circuit design and at the device level. Ping Yang and William Hunter have provided excellent technical guidance during the evolution of the work on ESD, and without their management support this work would not have been undertaken in the first place. Many of our colleagues here at Texas Instruments have done the groundwork, which has helped us expand our understanding in this area. We are especially grateful for the contributions of Kuen-Long Chen, David Scott, Vikas Gupta, Mike Chaine, Karthik Vasanth, Vijay Reddy, Tom Diep, Steve Marum, and Julian Chen, in this respect. In the area of device physics and modeling, the contributions of Mi-Chang Chang, Kartikeva Mayaram, Jue-Hsien Chern and Jerold Seitchik have been invaluable. We have had the pleasure of working closely with many academic institutions, and we thank Professors Henry Domingos at Clarkson University, Ken Goodson, Robert Dutton, Kaustav Banerjee at Stanford University, Chenming Hu at UC Berkeley, Elyse Rosenbaum and Steve Kang at University of Illinois at Urbana-Champain, and Jan Verweij, and Fred Kuper at the University of Twente, for their collaboration over the years. We greatly appreciate the significant contributions that Carlos Diaz and Sridhar Ramaswamy (University of Illinois at Urbana-Champain), Kaustav Banerjee (UC Berkeley), Xin Yi Zhang (Stanford), Sungtaek Ju (Stanford), and Gianluca Boselli (University of Twente), during their PhD studentships, have made to our understanding of the many issues related to ESD in silicon integrated circuits.

> Ajith Amerasekera Charvaka Duvvury Dallas, November 2001.

## Index

| Abrupt junction 76, 131, 133, 239, 249, 252, 253, 288, 289, 291, 292, 317  Adiabatic 336, 338  AEC 22, 24, 28, 29  Aluminium-silicon diffusions 304, 334  Aluminum-silicon 304  eutectic temperature 334  Analytical CDM-testing 38  Analytical models 4, 335, 336, 339, 341, 344, 375 | Avalanche breakdown 70, 71, 73, 75, 76, 81, 89, 90, 100, 131, 133, 138, 139, 141, 150, 157, 158, 160, 162, 236, 241, 242, 250, 288, 290, 298, 299, 329, 333, 350, 351, 354, 357, 359, 364, 368, 369, 373, 375, 383, 389  region 351  voltage 71, 75, 76, 90, 100, 133, 139, 141, 157, 160, 236, 250, 290, 298, 354, 357, 359, 364 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Anode 73, 76, 98–100, 150, 151, 157,                                                                                                                                                                                                                                                   | Background capacitance 23, 34                                                                                                                                                                                                                                                                                                     |

| 164, 218, 240, 297, 314, 315, 319,                                                                                                                                                                                                                                                     | Bakeable leakage current 238                                                                                                                                                                                                                                                                                                      |

| 373, 374                                                                                                                                                                                                                                                                               | Ballast resistance 96, 283                                                                                                                                                                                                                                                                                                        |

| to cathode spacing 99                                                                                                                                                                                                                                                                  | Barrier metal 304                                                                                                                                                                                                                                                                                                                 |

| Applications 6, 25, 35, 38, 39, 44, 45,                                                                                                                                                                                                                                                | Base charge factor 359                                                                                                                                                                                                                                                                                                            |

| 47, 57, 85, 98, 136, 138, 143, 144,                                                                                                                                                                                                                                                    | Base current 77–79, 84, 86, 89, 95,                                                                                                                                                                                                                                                                                               |

| 146, 153, 155–157, 162, 170, 171,                                                                                                                                                                                                                                                      | 120, 175, 207, 212, 282, 284, 285,                                                                                                                                                                                                                                                                                                |

| 179, 183, 189, 192, 215, 216,                                                                                                                                                                                                                                                          | 292, 310, 327, 344, 355, 369, 370,                                                                                                                                                                                                                                                                                                |

| 218–220, 223, 238, 247, 249, 326,                                                                                                                                                                                                                                                      | 376, 386                                                                                                                                                                                                                                                                                                                          |

| 350, 376, 395–397, 399                                                                                                                                                                                                                                                                 | Base transit time 21, 57, 80, 89, 314,                                                                                                                                                                                                                                                                                            |

| automotive 247                                                                                                                                                                                                                                                                         | 363                                                                                                                                                                                                                                                                                                                               |

| industrial 247                                                                                                                                                                                                                                                                         | Base transport factor 79, 352, 356                                                                                                                                                                                                                                                                                                |

| special 238                                                                                                                                                                                                                                                                            | Base-emitter resistance 219                                                                                                                                                                                                                                                                                                       |

| Arsenic implantation 290                                                                                                                                                                                                                                                               | Basic input protection scheme 156                                                                                                                                                                                                                                                                                                 |

| ASIC 377, 381                                                                                                                                                                                                                                                                          | BiCMOS 14, 95, 126, 157, 179–184,                                                                                                                                                                                                                                                                                                 |

| cell 381, 382                                                                                                                                                                                                                                                                          | 188, 218, 219, 223, 327, 368, 371,                                                                                                                                                                                                                                                                                                |

| library 377                                                                                                                                                                                                                                                                            | 383, 396                                                                                                                                                                                                                                                                                                                          |

| Avalanche 11, 12, 70, 71, 73–76, 81, 83–86, 88–90, 95–97, 100, 101,                                                                                                                                                                                                                    | BiCMOS protection circuits 184                                                                                                                                                                                                                                                                                                    |

| 123, 131, 133, 138, 139, 141, 150,                                                                                                                                                                                                                                                     | Bipolar 4, 24, 48, 55, 68, 77, 78, 80, 83–86, 88–92, 95, 96, 98, 101,                                                                                                                                                                                                                                                             |