# مكتبة عالم الإلكترون 4electron.com

إلى قارئ هذا الكتاب ، تحية طيبة وبعد ...

لقد أصبحنا نعيش في عالم يعج بالأبحاث والكتب والمعلومات، وأصبح العلم معياراً حقيقياً لتفاضل الأمم والدول والمؤسسات والأشخاص على حدِّ سواء، وقد أمسى بدوره حلاً شبه وحيدٍ لأكثر مشاكل العالم حدة وخطورة، فالبيئة تبحث عن حلول، وصحة الإنسان تبحث عن حلول، والموارد التي تشكل حاجة أساسية للإنسان تبحث عن حلول كذلك، والطاقة والغذاء والماء جميعها تحديات يقف العلم في وجهها الآن ويحاول أن يجد الحلول لها. فأين نحن من هذا العلم ؟ وأين هو منا؟

نسعى في موقع عالم الإلكترون <u>www.4electron.com</u> لأن نوفر بين أيدي كل من حمل على عاتقه مسيرة درب تملؤه التحديات ما نستطيع من أدوات تساعده في هذا الدرب، من مواضيع علمية، ومراجع أجنبية بأحدث إصداراتها، وساحات لتبادل الآراء والأفكار العلمية والمرتبطة بحياتنا الهندسية، وشروح لأهم برمجيات الحاسب التي تتداخل مع تطبيقات الحياة الأكاديمية والعملية، ولكننا نتوقع في نفس الوقت أن نجد بين الطلاب والمهندسين والباحثين من يسعى مثلنا لتحقيق النفع والفائدة للجميع، ويحلم أن يكون عضواً في مجتمع يساهم بتحقيق بيئة خصبة للمواهب والإبداعات والتألق، فهل تحلم بذلك ؟

حاول أن تساهم بفكرة، بومضة من خواطر تفكيرك العلمي، بفائدة رأيتها في إحدى المواضيع العلمية، بجانب مضيء لمحته خلف ثنايا مفهوم هندسي ما. تأكد بأنك ستلتمس الفائدة في كل خطوة تخطوها، وترى غيرك يخطوها معك ...

أخي القارئ، نرجو أن يكون هذا الكتاب مقدمة لمشاركتك في عالمنا العلمي التعاوني، وسيكون موقعكم عالم الإلكترون ww.4electron.com بكل الإمكانيات المتوفرة لديه جاهزاً على الدوام لأن يحقق البيئة والواقع الذي يبحث عنه كل باحث أو طالب في علوم الهندسة، ويسعى فيه للإفادة كل ساع، فأهلاً وسهلاً بكم.

مع تحيات إدارة الموقع وفريق عمله

4

www.4electron.com

موقع عالم الإلكترون www.4electron.com

#### INTRODUCTION

Electronics is heavily relied on by most other areas of electrical engineering. While there is a considerable body of theory in communications, controls, etc., these areas ultimately use electronics to actually implement the functions.

Electronic circuits use electronic devices to perform functions on signals such as amplification, filtering, rectifying, switching, etc.. Electronics has been a major topic of study in Electrical Engineering for nearly a century. Early electronic circuits used devices such as spark gaps and point-contact crystal diodes to perform signal processing. Later on, vacuum tubes were invented which made electronic communications and control systems widely available. In the late 1940's, semiconductor devices such as diodes and transistors became available which created an electronics revolution. With these changes in technology, the study of electronics did not change significantly, only the devices changed. The circuits and the methods did not change substantially.

The study of electronics can be roughly divided into two areas, devices and circuits. The study of devices is concerned with physical processes such as electron flow while the study of circuits emphasizes using the devices in applications and signal processing functions. The study of electronic circuits is further subdivided into analog, or linear, and digital, or switching, electronics. This course focuses on digital electronic circuits.

By far, the greatest use of digital electronic circuits occurs in digital computers. Logic circuits are widely available from simple logic gates in small-scale integrated (SSI) circuits to very complex digital functions in very large-scale integrated (VLSI) circuits. In almost all digital circuits, transistors and diodes operate in two modes, on or off, carrying current or not carrying current; in essence, a switch. We will look at how digital logic circuits operate and what the terminal characteristics and manufacturer's specifications mean. We will then look at how to go beyond the logic circuits with interfaces both at the inputs and outputs.

We begin this course with a brief discussion of semiconductor materials and pn junctions. This material is neither rigorously developed nor complete. A rigorous study of semiconductor electronics is left for later. However, to effectively use semiconductor devices, it is necessary to have a basic understanding of how they work.

Because electronic devices are non-linear, we will look at their terminal characteristics and make circuit models of the devices that will allow us to use to linear circuit analysis techniques to analyze the circuits. We will then look at application of semiconductor devices in switching circuits including logic gates, interface circuits, and special applications. Many electronic systems involve both analog and digital circuits and during this course, we will look at some of these cases requiring a mixture of applications. The ultimate test of understanding the material of this course will be found in the design exercises.

Introduction 1

#### Semiconductors

## THE ELECTRON IN ELECTRIC FIELDS

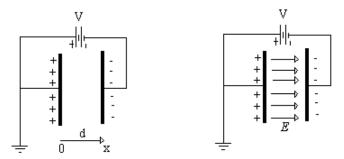

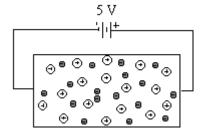

If we were to take two parallel plates and connect a voltage source across them as shown in Figure 1, an electric field would be set up between the plates. Neglecting fringing around the edges, the electric field would be uniform everywhere between the plates. The electric field strength would be

$$E = V/d (1)$$

where V is the applied voltage and d is the distance between the plates. Thus, the electric field strength *E* has the units volts per centimeter and is a vector quantity going from a positive charge to a negative charge. Note: CGS units are normally used in semiconductor physics - centimeters, grams, seconds.

Figure 1. Parallel plate with a voltage source connected between the plates.

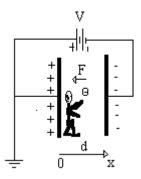

Now if a tiny person, let's call her Millie Micron, was able to carry an electron into the region between the plates and release it as shown in Figure 2, the electron would be attracted to the positive plate and repelled by the negative plate. The force on the electron would be

$$F_{X} = -qE_{X} \tag{2}$$

where q is the electronic charge. The negative sign occurs because the electron is accelerated in the negative x direction, toward the positive plate. Of course, the electron would obey Newton's laws and the acceleration,  $a_X$ , would be a function of the mass of the electron, m, and the force exerted by the electric field,

$$F_{X} = -ma_{X} \tag{3}$$

Figure 2. Millie releasing an electron within the electric field

As the electron accelerates, it gains kinetic energy. Just as with objects with mass in a gravitational field, the electron in an electric field has potential energy that can be converted to kinetic energy. The total energy then is

$$W = U + 1/2mv^2 \tag{4}$$

where U is the potential energy and v is the velocity. The energy associated with a single electron is quite small compared to units we normally work with so we use the units electron volts defined as moving one electron across a potential difference of one volt.

$$1 \text{ eV} = 1.602 \text{ x } 10^{-19} \text{ joules } (1 \text{ joule} = 1 \text{ watt second})$$

The electronic charge is  $1.602 \times 10^{-19}$  coulombs (ampere-seconds).

In our example, if the voltage source is 5 volts and Millie released the electron at the negative plate, the electron would gain five electron volts of energy as it fell to the positive plate. At that point it would have zero potential energy. Thus, at the point of release, the electron had a potential energy of 5 eV. This 5 eV would be converted to kinetic energy by the time it arrived at the positive plate.

To look at this another way, let's look at a plot of the electric potential within the field. We will assume the positive plate is grounded and at zero potential. The negative plate is at negative five volts with the potential changing linearly in between as shown in Figure 3. In this example, let's assume Millie is standing on the positive plate and throws the electron toward the negative plate. If she throws it gently, it will start with only a small kinetic energy which is soon converted to potential energy as the electron goes against the electric field. When all the kinetic energy is converted to potential energy, the electron has zero velocity. The electric field accelerates the electron back toward the positive plate. The effect is that the electron falls back to Millie and she catches it. If she then throws it again, but this time a little harder, it will go further, but will again fall back. Say, this is a neat game isn't it? This is similar to throwing a ball up a sloping roof and

catching it as it rolls back down. Just as with the roof, if Millie throws the electron hard enough, it will overcome the potential hill and escape. In this case, we must envision the negative plate as having lots of holes, like a wire screen, the electron can go through to escape; for example. This potential barrier concept will be used when we look at p-n junctions.

Figure 3. Illustration of the potential energy barrier.

#### ELECTRON EMISSION FROM THE METAL

Now, we can describe current flow between two metal plates. If a voltage is applied across the two metal conductors with just vacuum in between the two conductors, obviously no current flows between the two plates in the vacuum. There will be an electric field ( $E = V_s/x$ , where x is the distance between the two plates) dropped across two conductors. Charge builds up on each surface of the metal conductors that are facing each other. On one conductor, the cathode, electrons collect on the surface. On the other conductor, the anode, electrons are repelled from the surface, leaving the fixed metal ions at the surface. If a strong enough voltage (or a sufficiently high electric field) is applied, the electrons have a total energy equal to the vacuum energy,  $E_{vac}$ . The electrons at the surface of one metal conductor will be ripped out of the conductor and then move to the anode. And, current does flow across the vacuum!

This is called thermionic emission, a process by which tungsten filaments emit beams of electrons in cathode ray tubes for television, oscilloscope screens, and other instruments. The electric field required to rip the electrons out of the metal and into the vacuum is equal to  $q\phi_m$ , where  $\phi_m$  is the work function of the metal and q is the charge on an electron. Different metals have different work functions. So, some metals work better than others as "electron guns".

When additional energy is added to the system, for example by heating the metal, the kinetic energy of the electrons in the metal is increased and the electric field required for

thermionic emission is decreased. Thus, there are some "electron guns" that are called cold cathode emitters and others called hot filament emitters, denoting the temperature of the metal from which the electrons are escaping. The tungsten filament in your television is a hot filament emitter, running at over 2500K. Cold cathode emitters are used when a high temperature filament is impractical in the system. The cold cathode emitters are being researched for thin film displays and other applications where the system can not handle a large thermal gradients.

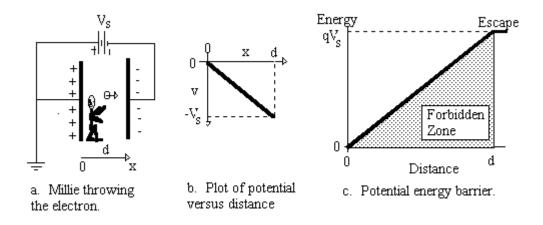

## CURRENT CONDUCTION IN METALS

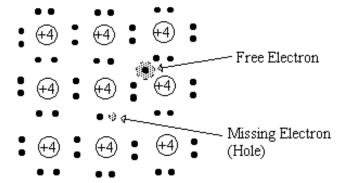

Metal atoms have one or more very loosely bound valence electrons. These are the electrons in the outer most orbital or electron shell, in an s or d orbital. At normal temperatures, the valence electrons have enough thermal energy to be easily separated from the metal atom and move randomly throughout the material. The metal atom, then, becomes a positively charged ion. Figure 4 is a two-dimensional representation of the situation where the electrons are free and the metal ions are immobile. The material still has zero net charge as there are still as many electrons in the metal as there are positive charges on the metal ions. In its random motion, an electron occasionally collides with a metal ion, but with its thermal energy, it is not captured and rebounds at a random angle. The motion of electrons in metal described here is similar to the motion of molecules in gas. Thus, it is called the electron gas model.

Figure 4. Metal with fixed ions and electrons in random motion.

If we were to average the motion or velocity of the electrons in the metal in Figure 4, we would find zero net motion and zero average velocity. However, if we were to apply a voltage between the ends of the metal conductor, a field would be set up between the ends of the conductor and the electrons would be accelerated toward the positive end. Thus, there is a drift of electrons in the conductor toward the positive end and a current results. This current is called drift current. The average speed at which the electrons drift is called the drift velocity,  $v_d$ . It seems as though the electrons might continue to accelerate in the field and reach very high velocities, but instead, the electrons soon collide with a fixed ion and recoil in a random direction, to again be accelerated by the field. Therefore, the electron's drift velocity reaches a maximum at some electric field and does not increase any further with increasing electric field. This is called the saturation velocity. The drift velocity under low field conditions, when the drift velocity is well below the

saturation velocity, is a function of the electric field and the physical properties of the conductor,

$$\mathbf{v_d} = \boldsymbol{\mu} E \tag{5}$$

where E is the electric field strength and  $\mu$  is the mobility of the electron in that material.

# **Electron Mobility**

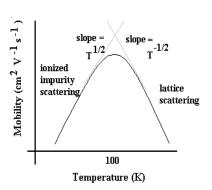

Mobility is a physical constant that describes the ease in which an electron can move through a material. The mobility is a function of temperature as well as the electric field. Thus, the speed of the electrons in the metal changes with temperature. The exact relationship between the change in mobility as a function of temperature is dependent on a number of material properties including the number of grain boundaries and how pure the metal is.

At 0K, there is no kinetic energy. Therefore, the valence electrons are localized in a metal atom. As the temperature is increased from 0K, there are some free electrons. However, their thermal energy is low. They interact with the metal ions and undergo Coulombic scattering events. In coulombic scattering, they lose some of their energy to the metal ion so their mobility is limited by the number of scattering events.

A macroscopic example of a similar problem would be if you shot an iron marble (the electron) through a grid of magnets (the metal ions), where there is considerable space between each of the magnets. The magnets are regularly spaced and fixed in position. When you shoot the marble, your aim is great – the path is clear from one end of the grid to the other. However, if the marble is rolled slowly (low kinetic energy), it is likely that its motion will be perturbed by the magnetic field of the magnets. At some point in its travel, the magnetic attraction may be strong enough to divert the forward motion of the marble and the marble will collide with the magnet. As you increase the speed at which you send the marble through the grid (increase the kinetic energy/temperature), the farther the marble will go through the grid before it gets attracted to one of the magnets.

As the temperature is increased further, the kinetic energy of the free electrons increases and the scattering events do not result in significant energy transfer. So, the mobility of the electron increases. However, as temperature increases significantly (to  $\sim 100 \text{K}$ ), the kinetic energy of the metal ions becomes large enough that they are vibrating with sufficient movement to impede the movement of the electrons. The scattering events are called lattice scattering. Again, there is energy transfer and the free electrons' mobility is decreased because of the scattering events. Unlike Coulombic scattering, the effect of

lattice scattering increases as the temperature increases, further decreasing the mobility of the free electrons.

Continuing with the macroscopic example: Now modify the grid so that the magnets are mounted on springs. As the grid is moved (because both the electrons and the metal ions have kinetic energy), the magnets "jiggle" back and forth. This reduces the amount of open area between each magnet. As the movement of the grid increases (an increase in temperature), the magnets jiggle further into the open areas and jiggle faster back and forth. This increases the likelihood that the marble will hit one or more of the magnets during its travel, reducing the distance that the marble can move through the grid.

## **Current Density**

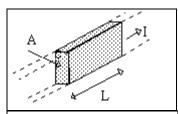

Figure 5. A section of a conductor with current I

Figure 5 shows a section of a conductor of length L and cross section A. Within this volume, there are N electrons. The number of free electrons, N, depends on the metal. If we apply a voltage, V, from end-to-end, the electrons will drift

towards the positive end with a drift velocity of  $v_d$ . The time required for the electronics to traverse the length, L, at an average drift velocity,  $v_d$  is

$$t_{t} = \underline{L}_{V_{d}}$$

(6)

All N of the electrons pass through the end of the section in time, t<sub>t</sub>. This electron drift constitutes a current I in amperes (coulombs/second).

$$I = \frac{qN}{t_t} \tag{7}$$

Substituting the transit time,  $t_t$ , into equation (7)

$$I = \frac{qNv_d}{L} \qquad \longrightarrow \qquad J = \frac{I}{A} = \frac{qNv_d}{LA}$$

(8)

where J is the current density which is defined as current over the cross sectional area.

The electron density is the number of electrons in a unit volume, n = N/LA. Thus

$$J = qnv_{\mathbf{d}} \tag{9}$$

# Conductivity

We can write current density in terms of the electric field by substituting  $v_d = \mu E$ ,

$$J = qn\mu E \tag{10}$$

We know that voltage is the electric field, E, times the distance over which the electric field is dropped (V = EL). Thus, resistance, R, can be rewritten as follows:

$$R = \frac{V}{I} = \frac{E L}{qn\mu E A} = \frac{L}{qn\mu A} = \frac{\rho L}{A}$$

(11)

In equation 11, we have related resistance of a sample to its shape and a parameter called resistivity,  $\rho$ . We define this parameter,  $\rho$ , as well as a second parameter, conductivity ( $\sigma$ ), which is the inverse of resistivity, as:

$$\sigma = 1/\rho = qn\mu \tag{12}$$

This result is an important equation. Conductivity is a function of the electronic charge, the (free) electron density, and the mobility of the electrons in the material. In metals, the free electron density is equal to the number of valence electrons times the density of atoms in the material that readily give up the valence electrons. Thus, mobility can be readily determined once the conductivity is found, which in turn is determined from the resistance measurement of a sample of the material. Also the physical dimensions of the metal are critical in determining its resistance. Resistance is a linearly proportional to the length of the metal and it is inversely proportional to its cross-sectional area.

## **Example:**

Aluminum has a density of 2.7 g/cm<sup>3</sup>, atomic weight of 27, and a resistivity of  $3.44 \times 10^{-6}$   $\Omega$ –cm. If Aluminum has three valence electrons, what is the mobility?

Avogadro's number is  $6.02 \times 10^{23}$  atom per mole. Thus, one mole of aluminum weighs 27 grams and has  $6.02 \times 10^{23}$  atoms. From this we get that one cm<sup>3</sup> of aluminum contains 0.1 moles or  $6.02 \times 10^{22}$  atoms. If each atom has three free electrons, there are  $18.06 \times 10^{22}$  free electrons per cubic meter. Thus we have

$$\sigma = qn\mu$$

or

$$\sigma = (3.44 x 10^{-6} \ \Omega \ cm)^{-1} = 1.602 x 10^{-19} \ Coul \ x \ 18.06 x 10^{22} \ free \ electrons/ \ cm^3 \ x \ \mu$$

$$\mu = 10 \ cm^2/Vs$$

So, if we have 3 meters of Aluminum wire, the length of a normal oscilloscope cable, and there is 5 volts dropped across the cable, the time that it will take an electron at one end of the cable to make it all the way to the other end of the cable (called transit time, t<sub>t</sub>) is 1800 seconds.

$$v_d = \mu E$$

$t_t = L/(\mu * E)$  (13)

$t_t = 300 \text{cm}/(10 \text{cm}^2/\text{Vs}*(5\text{V}/300 \text{cm})) = 1800 \text{ s}$

Not too speedy is it? This is one of several reasons why we don't transfer data using individual electrons, except over very short distances.

# **Resistance as a Function of Temperature**

Now, what happens to the resistance of a metal if we increase its temperature from room temperature (roughly 25°C) to, say, 125 °C, a commonly used maximum temperature of operation for certain devices and circuits? Look back at equation 11. Based upon our previous discussions, you know that the number of free electrons in the metal do not increase with increasing temperature. Of course, the length and cross-sectional area do increase slightly as the metal expands. For example, the length of an aluminum bar increases by 12 parts per million per degree C. Thus, a 1 meter long aluminum bar at room temperature will increase to a length of 1.012 meters.

However, the parameter that has most significant change with temperature is the mobility of the free electrons,  $\mu$ . And, the mobility decreases as the temperature increases to  $125^{\circ}$ C. Thus, the resistance of the metal increases with increasing temperature. If you look at the specifications for metal- and carbon-based resistors, you will see that their resistance is not a constant as a function of temperature, but increases. This increase in resistance with temperature can be minimized over specific temperature ranges through a careful design of the materials used and the physical structure of the resistor. So, even the selection of resistors needs to considered when you design of circuit – the selection will depend on your application.

## INTRINSIC SEMICONDUCTORS

Atoms in metals have relatively free valence electrons, which provide the carriers for conduction. Insulators are materials where there are virtually no free electrons, hence, no

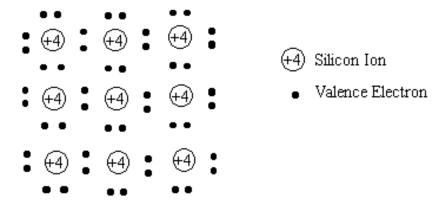

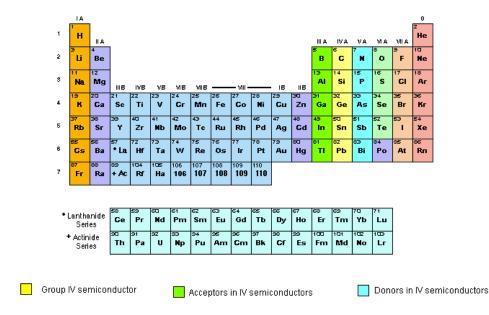

conduction. Semiconductors are in between. The most common semiconductor material is silicon, with germanium, gallium arsenide and indium phosphide used for some special purposes. As you can see from the periodic table, both silicon and germanium are group IV materials and have four valence electrons, two in the outer most s shell and two electrons in the p orbital. Gallium arsenide is a III-V compound where gallium has three valence electrons (two in the s orbital and one in the p orbital) and arsenic has five (two in the s orbital and three in the p orbital). A maximum of two electrons occupy the s orbital and a maximum of six occupy the p orbital. The number of valence electrons is important because these materials form crystalline structures and each atom shares electrons with its neighbors in covalent bonds to, in effect, fill each atom's outer shell.

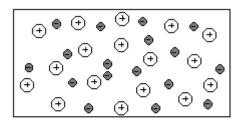

Because silicon is by far the most widely used semiconductor material, we will use it in our examples. A two-dimensional representation of the of the silicon structure is shown in Figure 6. Here the silicon atoms are arranged in regular rows and columns as in a crystal. Each atom shares four electrons with its four nearest neighbors. In the actual three-dimensional crystal, the structure is a tetrahedron and is called a diamond lattice. There are eight silicon atoms in each unit cell of the diamond lattice. A unit cell is the smallest volume that you can make that still has the same geometry of the overall crystal. In Si, the unit cell is a cube with dimensions of a = 0.545nm per side, where a is called a lattice constant.

Figure 6. 2-D representation of a silicon crystal.

As shown in the drawing, each electron is part of a covalent bond and is rather tightly bound. However, due to thermal agitation, an occasional electron has enough energy to break free from the bond and become free to roam throughout the crystal as shown in Figure 7. The only place with a positive charge that can capture the free electron is another broken bond. Thus, these free electrons can contribute to electrical conduction.

Figure 7. Silicon crystal with free electron and hole.

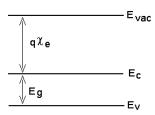

The free electrons are called conduction electrons. The conduction electrons reside in the conduction band, at an energy of  $E_{\rm C}$  and above. The remaining electrons that are bound to the atoms, the valance electrons, reside in the valence band, at energies of  $E_{\rm V}$  and below. The amount of energy required to free the electron is called the bandgap energy,  $E_{\rm g}$ . The bandgap energy arises from the interaction

of the atoms within the solid, the covalent bonds that results in the sharing of electrons between neighboring atoms. The energy required for thermionic emission of electrons from the semiconductor crystal, the emission of an electron from a semiconductor material into vacuum, is equal to  $q\chi_e$ , the charge on an electron times the electron affinity,  $\chi_e$ . The graph to the right is called an energy diagram and shows these different energy levels.

The difference between semiconductors and non-conductors, or insulators, is the size of the energy gap between the valence bands, and the conductions bands. If the energy gap is very small, then the material will conduct electric current easily. If the band gap is large, then it will be a non-conductor. Semiconductors typically have a band gap of about 1 electron volt, while insulators have a band gap of several electron volts. This definition is somewhat vague and should only be used as a general guideline.

# HOLE, THE MISSING ELECTRON

One interesting feature of the semiconductor is that the broken bond, called a hole, can also contribute to conduction. These holes reside at the top of the valence band, with an energy of  $E_V$  and are positively charged. Because the valence electrons and atoms have kinetic energy and the atoms are closely packed in a crystal, a valence electron can break its bond with a neighboring atom and complete the broken bond. Since there is now another broken bond on a different atom, a hole is now located on the neighboring atom. The results is that the hole has moved.

Just as the electron can be caused to drift in an electric field, so can the hole, although in the opposite direction because it has a positive charge. Thus, if an electric field is applied, the electrons move one direction and the holes the other. The result is that both contribute to current flow; the conventional current being in the direction of hole flow and opposite the direction of electron flow. This is unlike current flow in metals where only the free electrons contribute to current. The metal ions are fixed.

## **Electron-Hole Pair Generation and Recombination**

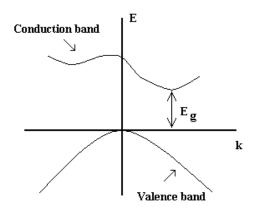

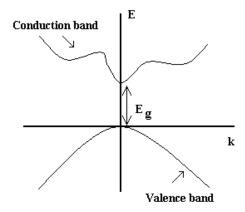

At any time a hole and a free electron may come together and recombine, thus removing the conducting elements. In fact, recombination occurs naturally and is an on-going process where hole-electron pairs are continuously created and annihilated. When the hole and free electron recombine, the free electron needs to lose the excess energy that enabled it to break free of its silicon atom. This amount of energy is equal or greater than the bandgap of the semiconductor  $(E_g)$ , the difference between  $E_C$  and  $E_V$  We use two quantum mechanical particles to describe how this energy is released. The energy may be released as phonons, a quantum of thermal energy or heat, or it may be released as photons, a quantum of light.

Phonons are usually released when the semiconductor is an indirect semiconductor. Two examples of an indirect semiconductor are silicon and germanium. In these semiconductors, the location of the minimum energy point in the conduction band is not directly above the maximum energy point in the valence band, when plotting the energy of the conduction band and valence band as a function of momentum, k. Since momentum has to be conserved when the electron recombines with the hole, the difference in momentum between the electron and hole is given

to another particle along with the excess energy. As a phonon has momentum and a photon does not, a phonon must also be emitted to conserve both energy and momentum.

Photons are usually released when the semiconductor is a direct semiconductor. An example of a direct semiconductor is gallium arsenide. In these semiconductors, the location of the minimum energy point in the conduction band is directly above the maximum energy point in the valence band, when the conduction band and valence band energies are plotted as a function of momentum, k. The only particle that can be released when the electron and hole recombine that has energy, but no momentum

is a photon. Therefore, light is emitted by direct semiconductors, while heat is emitted by indirect semiconductors, during electron-hole pair recombination. Thus, semiconductor laser diodes are composed of direct semiconductors such as gallium arsenide.

As mentioned, the generation of electrons and holes requires energy and when an conduction electron is created so to is a hole created. This energy can be thermal energy, heat, or the energy can come in the form of light, where the energy of the photon has to be equal to or greater than the bandgap of the semiconductor,  $E_{\rm g}$ . This process is more apparent in some applications such as photo-generated current in photoconductors.

## **CARRIER LIFETIMES**

In any semiconductor, hole-electron pairs are in a state of constant change. The total number of electrons and holes is a constant. However, individual electrons are sometimes found in the conduction band and other times are in the valence band. If a hole and an electron should meet, they will recombine - reducing the number of carriers. At the same time, the thermal energy of the crystal is exciting additional electrons to break the covalent bonds. At equilibrium, the number of pairs created is equal to the number that recombine. Thus, any free electron or any free hole will eventually recombine. Carrier lifetime,  $\tau$ , is a measure of how long any individual electron or hole will remain free.

How would we measure this lifetime? Let us do a thought experiment.

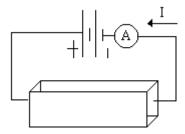

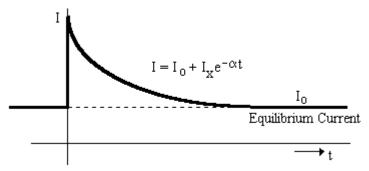

Assume we have a block of silicon at room temperature. Let's attach a voltage source across it and measure the current as shown in Figure A below.

Figure A: A block of silicon with a voltage source

Now we can determine the resistance of the silicon block. From the resistance, we can calculate the electron and hole densities. Then we can determine the total current contribution by the electrons and the holes.

Now let's use a powerful strobe lamp and create a flash of light with an energy greater than or equal to the bandgap of the semiconductor,  $E_{\rm g}$ . When this light falls on the silicon, the photons excite the electrons in the covalent bonds. Some of these electrons

will be excited into the conduction band and create hole-electron pairs in excess of the steady-state intrinsic level. These excess carriers are available for conduction so the current through the silicon block increases as the resistance of the silicon decreases. However, over time, the number of electron-hole pairs decreases because, the system will return to equilibrium without the continued light exposure (since it was only a pulse) providing the extra energy to free the electrons and create the holes. The excess electrons and holes will recombine and the electron and hole concentration returns to the equilibrium carrier concentration,  $n_i$ . Thus, the current will decrease in an exponential decay as shown in Figure B. We can measure carrier lifetime by measuring the rate at which the current decays. Carrier lifetime is one time-constant of the current pulse decay.  $(\tau = 1/\alpha)$  Note the similarity to the time constants for capacitive and inductive circuits.

Figure B. Current following a pulse of light.

This experiment also leads us to the idea of photoconductors and photodetectors.

# **Photoconductors and Photodetectors**

In a photoconductor, a voltage is dropped across the length of semiconductor. When a photon of light hits a covalent bond, it can transfer its energy to an electron by absorption, which can cause the covalent bond to disassociate and create a hole-electron pair. Because of the electric field across the semiconductor, the electron and hole move - in opposite directions. For as long as the photo-generated electron and hole exist, a current will flow in the photoconductor. When the electron and hole recombine, the current caused by the photogenerated carriers will cease. Of course, recombination occurs randomly recombining any hole with any electron, not necessarily the original pair. First of all, they are not monogamous. Secondly, they aren't even close to each other after a few femtoseconds, as they drift in opposite directions. In order for an electron to recombine with a hole to create a covalent bond between two Si atoms, they have to be within an atomic length of each other. In the case of Si, the atomic length is 0.235nm. As mentioned above, the average length of time that these photogenerated carriers will exist before they recombine is known as the carrier lifetime, τ.

The process of photon generation of electron-hole pairs can occur when the semiconductor is illuminated with photons that have an energy,  $E_{photon} = h\nu = hc/\lambda$ , greater than or equal to  $E_g$ , the bandgap of the semiconductor. h is Planck's constant and

is equal to  $6.63 \times 10^{-34} Js$ .  $\nu$  is the frequency of the photon.  $\lambda$  is the wavelength of the photon. Any photons with energy less than  $E_g$  will pass through the semiconductor. I.e., the semiconductor is transparent at wavelengths less than its bandgap. Silicon, which has a bandgap of 1.12 eV, is transparent to photons with a wavelength of less than  $1.1 \mu m$ , which is in the infrared wavelength region. Thus, Si absorbs visible light and looks grey. Gallium phosphide, on the other hand, has bandgap of 2.3 eV. Its bandgap is equal to the energy of green light and, thus, absorbs green and blue light. Therefore, gallium phosphide appears to be orange and somewhat transparent as red and yellow light passes through the semiconductor without being absorbed.

Table 1 is a list of the bandgaps of several semiconductors. Included in this list is diamond. Generally, diamond is considered to be an insulator. As can be observed, its bandgap energy is considerably larger than that of the other semiconductors listed. However, in special situations, diamond can be a semiconductor.

The general trend for bandgaps is that the larger (and heavier) the atoms are, the smaller the bandgap of the semiconductor. Thus, Si (28amu) has a larger bandgap than Ge (73amu). The bandgap is dependent on a number of factors including the strength of the bond between atoms in the crystal and the spacing between each atom (or length of each bond). As the temperature of the crystal increases, the bond length increases and the strength of the bond decreases. So, the bandgap is a function of temperature of the semiconductor, decreasing with increasing temperature.. A general formula for the bandgap as a function of temperature for any semiconductor follows the form of:

$$Eg(T) = Eg(0K) - \underbrace{A T^2}_{(B+T)}$$

Therefore, the lowest energy photon that the semiconductor can absorb changes with the temperature of the semiconductor. This change in bandgap energy as a function of temperature will also be important in understanding why the bias voltages of diodes and transistors vary with temperature.

Table 1 - Bandgap Energy

| Semiconductor    | Bandgap at 300K | Bandgap at 77K |

|------------------|-----------------|----------------|

| Silicon          | 1.12eV          | 1.17eV         |

| Gallium Arsenide | 1.424eV         | 1.508eV        |

| Germanium        | 0.661eV         | 0.733eV        |

| Indium Phosphide | 1.35eV          | 1.414eV        |

| Diamond          | 5.46eV          | 5.48eV         |

Typical applications that rely on photogenerated carriers are in opto-isolators and opto-interrupters where the light source is turned on and off or where an object interrupts the light beam. The speed of detection and extinction is limited by the lifetimes of the carriers, typically nanoseconds to a few microseconds.

## CARRIERS IN INTRINSIC SEMICONDUCTORS

In semiconductors, it is conventional to use the symbol n for the electron density, the number of electrons per cm<sup>3</sup>, and p for the hole density or the number of holes per cm<sup>3</sup>. In the intrinsic semiconductor, holes and electrons are created in pairs, n = p and the common symbol is usually designated  $n_i$ , where the subscript indicates intrinsic material, or pure silicon.  $n_i$  is also known as the intrinsic carrier concentration.

$$n_i^2 = np \tag{14}$$

The number of thermally generated electron-hole pairs is a function of the semiconductor material and its temperature.

$$n_i = (N_c N_v)^{1/2} \exp(-E_g/2kT)$$

(15)

where:

$$N_{c} = 2 \left( \frac{2 \pi m_{e} kT}{h^{2}} \right)^{3/2}$$

(16)

$$N_{v} = 2\left(\frac{2\pi m_{h}kT}{h^{2}}\right)^{3/2}$$

(17)

$m_e$  and  $m_h$  are the effective mass of the electron and hole in the semiconductor, respectively. Strangely enough, these values can be very different from the mass of an electron in vacuum,  $m_o = 9.1 \times 10^{-31}$  kg. The effective mass for electrons and holes for a number of semiconductors are given in Table 2.

Table 2

| Semiconductor    | Electron Effective Mass, m <sub>e</sub> | Hole Effective Mass, m <sub>h</sub> |

|------------------|-----------------------------------------|-------------------------------------|

| Silicon          | 1.18 m <sub>o</sub>                     | 0.81 m <sub>o</sub>                 |

| Germanium        | $0.55 \text{ m}_{o}$                    | $0.36 \text{ m}_{o}$                |

| Gallium Arsenide | $0.063 \text{ m}_{o}$                   | 0.48 m <sub>o</sub>                 |

# **Temperature Dependence of Hole-Electron Concentration**

As the temperature increases, the electrons get more energetic and the probability that an electron is excited into a higher energy state, the conduction band, is increased. Thus, the number of electrons in the conduction band is increased and the number of hole-electron pairs is increased. Finally, the conductivity is increased. The equation describing  $n_i$  specifically for intrinsic silicon is

$$n_i = p_i = 4.8x10^{15} T^{\frac{3}{2}} e^{(\frac{-5797E_g}{T})} / cm^3$$

T is the temperature in degrees K, and  $E_g = 1.12$  eV, the energy gap in silicon.

This equation gives  $n_i = 1.5 \times 10^{10} \text{ per cm}^3$  at room temperature, 300 degrees K, or 27 degrees C. At 60 degrees C,  $n_i = 10^{11} \text{ per cm}^3$

We can use this characteristic to build temperature sensitive devices to measure temperature or to compensate for temperature changes such as thermistors.

# CURRENT IN INTRINSIC SEMICONDUCTORS

Conduction due to the electrons is

$$J_{n} = qn\mu_{n}E \tag{18}$$

where the subscript n indicates electrons. Similarly, the hole conduction is

$$J_{p} = qp\mu_{p}E \tag{19}$$

where this time, the subscript p indicates holes. As the different physical properties of the electron and hole are different, the mobilities and effective masses of the electrons and holes are not the same. Therefore, the hole current and electron current need to be calculated separately and then added together. The total current density is

$$J = J_n + J_p = qn\mu_n E + qp\mu_p E = q(n\mu_n + p\mu_p)E$$

(20)

$$= qn_i(\mu_n + \mu_p)E \tag{21}$$

Conductivity in intrinsic material is

$\sigma_i = q n_i (\mu_n + \mu_p)$  [Be careful here, this equation applies only for intrinsic material

where

$$n = p = n_i J$$

(22)

It is of interest at this time to calculate the conductivity of intrinsic silicon and compare it to the conductivity of aluminum.

Example: Calculation of conductivity of intrinsic silicon.

Several properties of silicon at 300K (room temperature) are given in Table 3. From these properties we see that the intrinsic carrier density is  $1.45 \times 10^{10}$  carriers per cm<sup>3</sup>, the mobilities of electrons and holes are 1500 and 475 cm<sup>2</sup>/Vs, respectively. Conductivity is then

$$σi = 1.602 x 10-19 {coul}X 1.45 x 1010 {cm-3} X (1500 + 475) {cm2/Vs}$$

$$= 4.59 x 10-6 (Ω cm)-1$$

| TABLE 3<br>PROPERTIES OF SILICON           |                      |                                                     |                       |  |  |

|--------------------------------------------|----------------------|-----------------------------------------------------|-----------------------|--|--|

| Atomic Number                              | 14                   | $\mu_{\rm n}$ at 300° K (cm <sup>2</sup> /Vs)       | 1500                  |  |  |

| Atomic Weight                              | 28.1                 | $\mu_{\rm p}$ at 300° K (cm <sup>2</sup> /Vs)       | 475                   |  |  |

| Density (gm/cm <sup>3</sup> )              | 2.33                 | $n_i$ at 300° K (cm <sup>-3</sup> )                 | $1.45 \times 10^{10}$ |  |  |

| Atoms/cm <sup>3</sup>                      | $5.0 \times 10^{22}$ | $D_n$ at $300^{\circ}$ K (cm <sup>2</sup> /s)       | 34                    |  |  |

| $\rho_i$ at $300^{\circ}$ K ( $\Omega$ cm) | $2.30 \times 10^5$   | $D_{\rm p}$ at $300^{\rm o}$ K (cm <sup>2</sup> /s) | 13                    |  |  |

| Dielectric constant $\varepsilon_r$        | 11.7                 | Electron affinity $\chi_e$                          | 4.05eV                |  |  |

Compare this with the conductivity of aluminum at  $2.9 \times 10^5 \, (\Omega \, \text{cm})^{-1}$ . Obviously, intrinsic silicon is not nearly as good a conductor as aluminum. We will see shortly, however, that adding impurities to silicon can change its conductivity by several orders of magnitude.

#### EXTRINSIC SEMICONDUCTORS

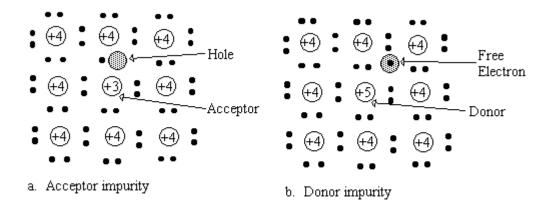

In order to increase the number of free electrons or holes in a semiconductor, impurities are introduced. There are two types of impurities used, donors and acceptors. In Si, donor atoms typically have 5 valence electrons. In the crystal structure, four are bound in covalent bonds with adjacent silicon atoms. The remaining valence electron is easily disassociated, thus donating an electron for conduction. Only about 5 to 50meV are required to remove these remaining valence electrons. Since the amount of thermal

energy available is equal to kT, where k is Boltzman's constant  $(8.6 \times 10^{-5} \text{eV/K})$  and T is temperature in Kelvin. At room temperature (~300K), the kinetic energy available to the system is ~25meV, which is greater than the average energy required to ionize an impurity in a semiconductor. Thus, essentially all of the extra electrons on the donor atoms are free conduction electrons at room temperature.

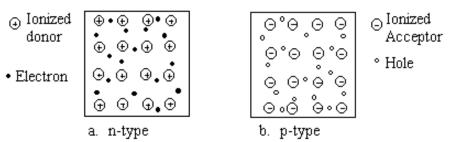

Acceptor atoms usually have 3 valence electrons, and in the crystal structure, leave a valence vacancy which can trap an electron, thereby creating a hole for conduction. The energy required for this is typically slightly more than what is required to ionize a donor - 10-100meV. However, most of the acceptors are ionized (created a hole) when the temperature of the semiconductor is above 100K. Pictorial examples are shown in Figure 8. A periodic table which identified the possible donor and acceptor atoms in IV semiconductors is below.

Silicon with an excess of free electrons is called n-type while silicon with an excess of holes is called p-type. Typical donors are pentavalent atoms: antimony, phosphorous, and arsenic. Typical acceptors are trivalent atoms: boron, gallium, and indium. In GaAs and other III-V semiconductors, column II atoms are acceptors and column VI atoms are donors. Column VI atoms in GaAs are donors if they occupy a Ga site and are an acceptor if they occupy an As site. Thus, Column IV atoms (e.g., Si and Ge) in III-V semiconductors are called amphoteric dopants, meaning that they can act as either a donor or an acceptor.

Figure 8. Silicon with impurities.

# Periodic Table of the Elements

#### Periodic Table

These impurities are introduced into the silicon either during crystal growth or after a crystal of pure silicon has been grown and sliced into wafers. Silicon wafers are grown by melting a large quantity of noncrystalline silicon in a carbon crucible. The melting point of silicon is 1460°C. To dope the silicon with impurities, an appropriate amount of donor or acceptor atoms are mixed into the melted silicon. A small single crystal of silicon, called a seed crystal, is then lowered slowly into the silicon melt, but pulled out before it completely melts. Because of silicon's high surface tension, some of the liquid silicon is pulled out with the seed crystal and begins to cool and solidify. The solidified silicon using the structure of the seed crystal as a template and, thus, grows as a single crystal. The seed crystal is continued to be pulled away from the silicon melt such that there is alway some liquid silicon wetting the solidified silicon. The solidified silicon is called a boule. Once the growth process is complete, the boule is sliced into wafers, which are then polished to remove the mechanical damage from the sawing process.

The impurities can also be selectively introduced into the silicon wafer via diffusion or ion implantation. Typically, the wafer is allowed to oxidize to create a surface film of silicon dioxide, SiO<sub>2</sub>. Then some of the SiO<sub>2</sub> is etched away in places where n-type or p-

type regions are wanted. During a diffusion, the wafers are heated and exposed to high concentrations of the desired impurity. The impurity diffuses through the openings in the SiO<sub>2</sub> into the silicon displacing an occasional silicon atom in the crystal lattice. Upon cooling, the impurity atoms freeze in place, creating the n- or p-type regions. In ion implantation, a beam of high energy ions (ionized donor or acceptor atoms) bombard the surface of the silicon wafer. The SiO<sub>2</sub> prevents the ions from reaching the silicon surface. However, they penetrate the silicon where ever the SiO<sub>2</sub> has been removed. The silicon wafer is then heated to 700-1000°C to give the ions enough energy to incorporate into the silicon lattice.

Only those impurities that occupy a site in the crystal lattice where a silicon atom would have been act as donors or acceptors and are called substitutional impurities. Those impurities that are in the silicon crystal but do not sit on a silicon site do not contribute a electron or hole to the semiconductor and are call interstitial impurities. Interstitial impurities, though not electrically active, reduce the mobility of the electrons and holes in the semiconductor as they will act as scattering sites as the electrons and holes move through the crystal

#### **Carrier Concentrations**

In intrinsic material, hole-electron pairs are thermally generated. These hole-electron pairs can also recombine. This process of generation-annihilation goes on continuously with the number of pairs at some equilibrium, where the number of electrons equals the number of holes. The average amount of time a hole or electron is free is called the carrier lifetime,  $\tau$ . In n-type extrinsic material, there is no hole corresponding to the donated electron. There are still thermally generated hole-electron pairs, but the equilibrium is shifted so that there are fewer thermally generated carriers.

Within the extrinsic semiconductors, two processes take place which contribute to the carrier concentration. Hole-electron pairs are created by thermal agitation just as in the intrinsic case. In addition, the impurity atoms are virtually all ionized creating the corresponding carriers. Usually, the doping level is high enough that the extrinsically provided carriers predominate over the thermally generated carriers.

If both types of impurities are present simultaneously, they simply cancel each other out; an acceptor ion captures the excess electron provided by a donor ion. This is called compensation. Only the excess impurity concentration contributes to the conductivity. In most cases, one type of impurity predominates, creating an extrinsic material of the desired type. In perfectly compensated material, the concentration of electrons equals the concentration of holes and both are equal to the intrinsic carrier concentration,  $n_i$ . But, the mobility of the electrons and holes is lower than in intrinsic material because of the larger number of impurity ion to scatter with.

Because of the physics of hole-electron pair formation, the total number of free carriers in the semiconductor is controlled by the mass-action law, equation 16 which is  $\mathbf{np} = \mathbf{n_i}^2$ . Thus, in an n-type material, the number of electrons is increased due to the donor ions, thereby causing the number of free holes to be reduced. In the n-type material, electrons are the majority carrier. Similarly in p-type material, holes are the majority carrier. Let  $N_D$  represent the concentration of donor ions and let  $N_A$  represent the acceptor concentration. The material must maintain charge neutrality so that the total number of positive charges will equal the total number of negative charges.

$$N_D + p = N_A + n \tag{23}$$

Donors give up electrons so they become a positively charged ion. Ionized acceptors have a negative charge as they have captured an extra electron. In an uncompensated n-type material,  $N_A = 0$  and because virtually all the donors will be ionized at most temperatures,

$$N_D + p = n \tag{24}$$

Here the free electrons, n, have two sources; donors,  $N_D$ , and thermally created hole-electron pairs, p. In all but extremely lightly doped materials, the number of impurity atoms is a much greater in concentration than is the intrinsic electron concentration,  $n_i$ . In other words,  $N_D >> n_i$ . Thus,  $n \cong N_D$ . We can find the hole concentration from the mass action law  $(np = n_i^2)$

$$p = n_i^2 / n \cong n_i^2 / N_D \tag{25}$$

Likewise, when there is p-type semiconductor, the number of holes is determined by the number of acceptor atoms in the material. Thus,  $p \cong N_A$ . Again, we can find the electron concentration from the mass action law

$$n = n_i^2/p \cong n_i^2/N_A$$

(26)

Now let's look at the conductivity of a doped n-type material.

Example: Conductivity of doped material

Assume silicon is doped with donors so that  $N_D = 5 \times 10^{12}$  atoms/cm<sup>3</sup>. Determine the conductivity of the material.

The electron density  $n \approx N_D$  and we can find the hole density from the mass action law.

$$p = (1.45 \times 10^{10})^2 / 5 \times 10^{12} = 4.21 \times 10^7 / cm^3$$

(Note that  $p = 4 \times 10^7$  are all thermally generated holes. There are an equal number of thermally generated electrons, but this number of thermally generated electrons is insignificant when compared to the number of donors that contributed electrons.)

The conductivity then is

$$\sigma = q(n\mu_n + p\mu_p)$$

However, the added donors do more than increase the number of electrons in the material, they also decrease the mobility of the electrons and holes. This is because they act as Coulombic (or ionic) scattering sites (see the figure in the discussion on electron mobility in metals). The donor atons also slightly distort the unit cell because they are not exactly same size as the silicon atom they replace and the bonds that they form with the adjacent silicon atoms are not the same length as the Si-Si bonds.

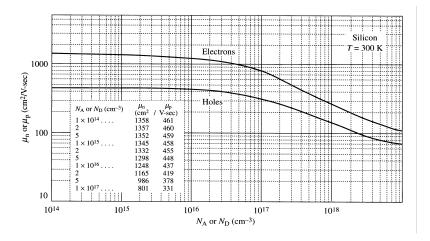

The figure above shows the relationship between mobility and doping levels for both n-type and p-type silicon. For the doping level in the example, the donor ions do not significantly change the mobility of the carriers. Therefore, the the mobility of the holes and electrons are equal to the value of intrinsic silicon. The lower values of mobility would need to be used when calculating the conductivity of more heavily doped material,  $10^{15}$  cm<sup>-3</sup> to  $10^{18}$  cm<sup>-3</sup>, which are typical doping levels for diodes and transistors.

Thus, for our example,

$$\sigma = 1.602 \times 10^{-19} (5 \times 10^{12} \times 1500 + 4.21 \times 10^{7} \times 475)$$

$$\sigma = 1.602 \times 10^{-19} (7.5 \times 10^{15} + 2.00 \times 10^{10})$$

$$= 1.2 \times 10^{-3} (\Omega \text{cm})^{-1}$$

This conductivity is almost 3 orders of magnitude greater than for intrinsic silicon.

Note that the electron density is five orders of magnitude greater than the hole density which means that the holes contribute very little to the conductivity. It can be seen from this example that if the doping level is significantly higher than the intrinsic electron/hole density, the majority carrier does most of the conducting in the material and that the conductivity is directly proportional to the doping level.

#### Fermi Level

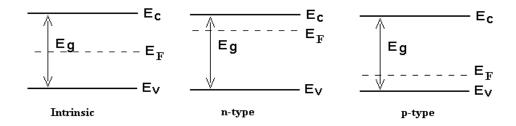

When drawing a energy band diagram, we indicate what type the material is (n type or p type) by the placement of the Fermi level,  $E_F$ . The Fermi level is an imaginary energy level. When it is positioned halfway in between the conduction band and valence band, the material is intrinsically doped or evenly compensated. When the Fermi level is close to the conduction band, the material is n-type. The closer the Fermi level is to the conduction band, the more heavily doped is the material - the larger  $N_D$  is. When the Fermi level is close to the valence band, the material is p-type. The closer the Fermi level is to the valence band, the more heavily doped is the material - the larger  $N_A$  is.

No matter what the temperature of the semiconductor is, the Fermi level is halfway between the conduction and valence bands for an intrinsic semiconductor. However as the temperature increases, the Fermi level in a doped semiconductor moves towards the middle of the bandgap. The reason for this is that the intrinsic carrier concentration increases significantly with temperature. Thus, the extrinsic carrier concentration becomes less important as the temperature increases. Another way to express this is that as silicon becomes intrinsic as the temperature increases because  $n_i > N_D$  or  $N_A$ . This is one reason why there is a maximum temperature of operation for most semiconductor devices.

### CONDUCTION BY DIFFUSION

So far we have talked exclusively about conduction by drift of carriers in an electric field. However, conduction by diffusion is important in some cases. Diffusion result from the natural tendency of most particles move from regions of high concentration to regions of

lower concentration. That is, diffusion is driven by concentration gradients while drift is driven by electric fields. Everyone has experienced an example of diffusion where a person opens a bottle of perfume (or a package of fish), in a few minutes, a different person in another part of the room can smell it.

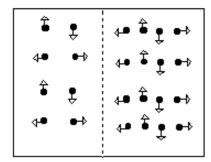

The reason this diffusion happens is illustrated in Figure 9. In this figure, we have simplified the situation by assuming only four possible directions of motion: up, down, right, and left. In random motion, one fourth of the particles will be going in each direction. Now the left side of the volume has one half the density of the right side. Thus, there are twice as many particles going left across the boundary as there are going right in any period of time. In a short time then, there will be more particles on the left than as shown in the diagram. After while, the two sides will have the same density and the diffusion current will stop. The random motions will average out on both sides.

Figure 9. Illustration of diffusion

For n-type material, the diffusion current is given by

$$J_{n} = qD_{n} \frac{dn}{dx}$$

(27)

where  $D_n$  is the diffusion constant. Note that if dn/dx has a positive slope (rises to the right), the concentration is higher to the right and electrons will diffuse to the lower concentration, to the left. Because the electrons have a negative charge, the current will be to the right, or in the positive x direction. Thus, if we look at diffusion current in a p-type material,

$$J_{p} = -qD_{p} \frac{dp}{dx}$$

(28)

Here the negative sign reflects the fact that the holes will diffuse to the left causing current in the negative x direction.

The diffusion constant of a hole or electron is related to that carrier's mobility by the

following equation:

$$D/\mu = kT/q \tag{29}$$

If we have both an electric field and a concentration gradient, the total current density is the sum of the drift current and the diffusion current densities.

$$J_{n} = q\mu_{n}nE + qD_{n}\frac{dn}{dx} \qquad \text{for electrons}$$

(30)

and

$$J_{p} = q\mu_{p}pE - qD_{p}\frac{dp}{dx} \qquad \text{for holes}$$

(31)

The total current density is

$$J = J_{n} + J_{p}$$

$$= q(n\mu_{n} + p\mu_{p})E + q(D_{n}\frac{dn}{dx} - D_{p}\frac{dp}{dx})$$

(Drift) (Diffusion) (32)

# THE pn JUNCTION

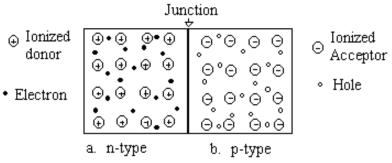

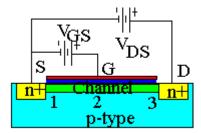

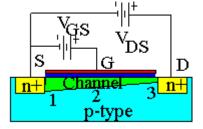

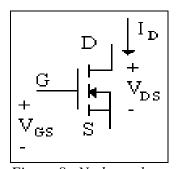

We have now set the stage for looking at the p-n junction, the basis for most semiconductor devices. Figure 10 shows blocks of n-type and p-type material. In these drawings, only the donor and acceptor ions are represented along with the resulting free electrons and holes, the majority carriers in each material. The minority carriers, the holes in the n-type material and the electrons in the p-type materials, are not shown here to keep from cluttering up the diagram, especially since there are so few of them

Figure 10. n-type and p-type blocks of material.

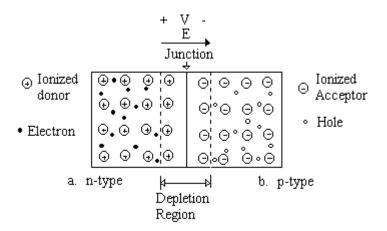

In each block in Figure 10, the positive and negative charges balance. Now if we bring those blocks together as shown in Figure 11, we still have charge neutrality, but we have

a concentration step dislocation. We have a high concentration of electrons to the left of the junction and a high concentration of holes to the right.

Figure 11. p-n junction at moment of contact.

The donor and acceptor ions are fixed by the crystal lattice, but the holes and electrons are free to move. These carriers diffuse to the regions of lower concentration until the device comes to equilibrium shown in Figure 12.

Figure 12. p-n junction at equillibrium

In Figure 12, some of the electrons diffused over into the p-type material and some of the holes diffused over into the n-type material. These become minority carriers and are not shown. In fact, outside the depletion region, most of the excess minority carriers recombine with majority carriers and thus, are annihilated. Obviously, the carriers closest to the junction were the first to migrate by diffusion. This migration left behind some charged ions in the area marked as the depletion region. These charged ions create an electric field with the positive side in the n-type material and negative side in the p-type material. This field is essentially a potential hill which repels further migration. The carriers left behind, beyond the depletion region, still have thermal energy and move randomly in the area. If an electron had enough energy to overcome the potential barrier, and was moving in the proper direction, it would pass across the junction. This electron

would leave another charged ion behind, increasing the potential barrier, making it harder for others to cross.

Now going back to the minority carriers. These are not shown in the diagram, but they too are distributed throughout their respective areas outside the depletion region. This distribution means that some are near the electric field at the edge of the depletion region, but instead of being repelled by it, they are attracted by it and are pulled across the junction. This act has the opposite effect on the barrier height, essentially neutralizing an ion, and lowering the barrier.

The result is a continuous motion of charges back and forth across the junction at equilibrium. Minority carriers diffuse to the junction, are swept across the depletion region. This causes the potential barrier to be lowered which allows majority carriers to diffuse against the barrier. The charge motion is random, with the total current balancing to zero. However, at any one instant in time, there is a measurable current flowing across the p-n junction, even with zero voltage applied. The currents are quite small compared to other currents we will be looking at later. However, these currents are important in the operation of many devices. For example, these currents contribute to the dark current of a zero biased photodetector.

It is often of interest to consider what happens if the doping levels are not the same on both sides of the junction. First, we note that charge neutrality in the device must be maintained and in fact is maintained both in the depletion region and in the non-depleted regions of the n-type and p-type materials. The depletion region is charge neutral, with the positive ions balancing the negative ions. Thus, if one of the regions has a higher concentration of doping ions, that part of the depletion region will be narrower than that in the region with lower doping. Similarly, if both regions had higher doping, the depletion would be narrower and the field gradient or field strength would be higher although the total potential difference would be the same. The depletion width, W, can be calculated using the following equation:

$$W = \left(2 \frac{\varepsilon_r \varepsilon_o}{q} \frac{N_A + N_D}{N_A N_D} (V_{bi} - V_a)\right)^{1/2}$$

(33)

where  $\epsilon_r$  is the relative dielectric constant which is between 10-12 for most semiconductors,  $\epsilon_o$  is the permittivity of free space (8.85 x10<sup>-14</sup> F/cm),  $V_{bi}$  is the built-in voltage of the p-n junction, and  $V_a$  is any externally applied voltage across the p-n junction.

The built-in voltage of the p-n junction is equal to the electric field developed across the depletion width times the width of the depletion layer. It is equal to:

$$V_{bi} = \frac{kT}{q} \ln \left( \frac{N_A N_D}{n_i^2} \right)$$

(34)

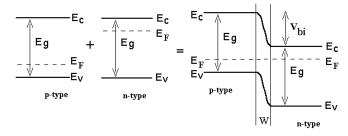

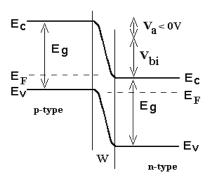

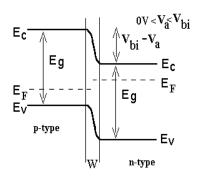

One can see how the built-in voltage is developed when a p-type region is in contact with an n-type region by using the energy diagrams and the concept of continuity of the Fermi level. Continuity of the Fermi level means that, at zero bias, we redraw the energy diagrams of the p-type and n-type regions so that the Fermi levels of the two materials are at equal positions. Thus, the electrons in the n-type material need to gain enough energy, about  $V_{bi}$ , to overcome the energy barrier, the "hill" in the energy diagram, in order to move into the p-type material. And, the holes also need to gain energy to flow into the n-type material. [Increasing energy for a hole is negative energy.]

As can be seen from equation 33, as the voltage across the junction increases (i.e, the junction is reverse biased,  $V_a < 0V$ ), the depletion region width increases as well. Furthermore, the Fermi level of the p-type material is no longer drawn at the same energy as the Fermi level as the n-type material and the energy barrier for the holes to flow into the n-type material and electrons to flow into the p-type material increases. Changes in

the width of the depletion region will result in charge transfers, similar to those in capacitors. This phenomenon give s rise to the concept of junction capacitance, C<sub>i</sub>.

$$C_{j} = \varepsilon_{r} \, \varepsilon_{o} \, A/W \tag{35}$$

where A is the cross-sectional area of the p-n junction.

At higher doping levels, the depletion width is thinner and we get a higher capacitance at

the junction. In some cases, this higher capacitance can cause problems with device speeds when there are large voltage changes, but also the narrow depletion region means carriers crossing the region take less time (the transit time, t<sub>t</sub>, is small) and that switching speeds can be increased if the change in voltage is low. In general, there is a speed/current trade-off in the design of these junctions. We will see the results of this trade-off later in this course. The design of semiconductor devices is a fascinating subject, but requires material beyond the scope of this course.

In forward bias,  $V_a > 0V$ , the depletion region decreases, the junction capacitance increases, and the electrons in the n-region need less excess energy to flow into the pregion/the holes in the pregion needs less excess energy to flow into the n-region. From the discussion thus far, you would expect that when the externally applied voltage,  $V_a$ , is equal to the built-in voltage,  $V_{bi}$ , the junction capacitance becomes infinite. But, of course, this doesn't happen because the resistance of the junction becomes zero, which shorts the junction capacitor.

#### **DIODES**

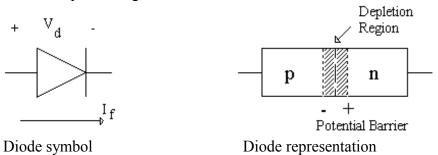

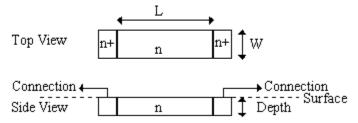

A pn diode is the simplest junction semiconductor device. A simple representation of a a p-n junction is shown below. At the junction, a depletion region forms where all free carriers have gone away, leaving the fixed donor and acceptor ions which cause a static field. This static field just balances the tendency of the majority carriers on either side to diffuse into the depletion region.

In the steady-state case, there are several processes going on all the time that result in zero net current flow. (1) Majority carriers, holes from the p region and electrons from the n region diffuse into the depletion region. A few are energetic enough to cross the potential barrier,  $V_{bi}$ , and result in a current flow. Balancing this flow, (2) minority carriers, holes in the n region and electrons in the p region diffuse into the depletion region. The field sweeps them across the region into their respective majority regions. (3) Hole-electron pairs are continuously created in the depletion region by thermal agitation. These carriers are swept by the field from the depletion region. (4) Recombination of hole-electron pairs balances the thermal generation to maintain charge neutrality.

The previous discussion has assumed no external connections. Let us now consider what

happens when a short circuiting wire is connected externally to the two ends of the device. Actually, the experiment is a big flop, nothing happens. A little thought will reveal to us that while there is contact potential difference between the two different semiconductor materials, there is also a contact potential difference between the wire and the semiconductor materials at both ends. It should come as no surprise that these contact potentials cancel each other; the sum of the contact potentials around the circuit is zero.

If a forward voltage is applied to the diode, positive to the p material and negative to the n material, the potential barrier is decreased - by the value of the applied voltage if we

assume that there are no resistive voltage drops in the p and n regions. Then, majority carriers diffusing into the depletion region can more easily overcome the potential barrier. Because both holes and electrons are involved and have opposite charges, the result is a net current flow from left to right. In many cases, the doping levels will be unbalanced (either  $N_D >> N_A$  or  $N_A >> N_D$ ) such that either the hole current or electron current will dominate and the other will be ignored.

If a reverse voltage is applied to the diode, the additional voltage across the depletion region will widen it. There will also be a very small reverse current, called the reverse saturation current. This current arises from the minority carriers diffusing to the depletion region and being swept across. This current is no longer balanced by forward diffusion of majority carriers because the potential barrier is now much higher and is maintained by the external source.

$$I_{S} = qA \left\langle \frac{D_{n}}{L_{n}} \frac{n_{i}^{2}}{N_{A}} + \frac{D_{p}}{L_{p}} \frac{n_{i}^{2}}{N_{D}} \right\rangle$$

(36)

where  $D_n$  is the diffusion constant of minority electrons in the p region,  $L_n$  is the diffusion length of these minority electrons,  $D_p$  is the diffusion constant of minority holes in the n region, and  $L_p$  is the diffusion length of these minority holes. The minority carrier diffusion length is related to both the minority carrier diffusion constant and the lifetime of these minority carriers,  $\tau$ .

$$L = (D \tau)^{1/2} \tag{37}$$

It is the change in potential that is responsible for the difference in resistance of a diode when measured using a digital multimeter. Try this yourself, measure the resistance of a diode with the probes connected in one way. Then, measure the resistance again after switching the probes to the opposite terminals of the diode. One measurement will be very high, usually 1- $10M\Omega$ . The other resistance measurement will be much lower. The

reason for this is that the multimeter applies a very small voltage to the component under test. In one probe configuration, the diode is slightly reverse biased and a extremely small amount of current flows. In the other configuration, the diode is slightly forward biased and a much larger current flows.

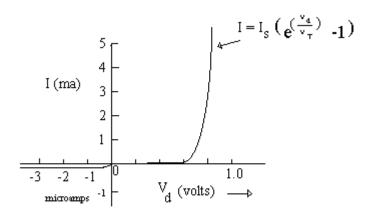

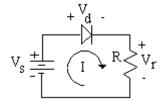

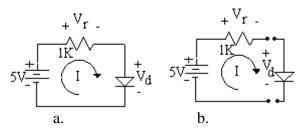

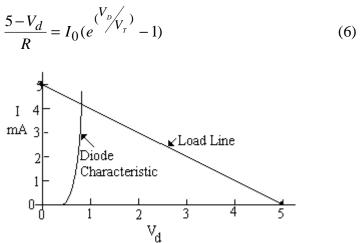

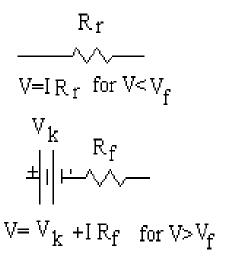

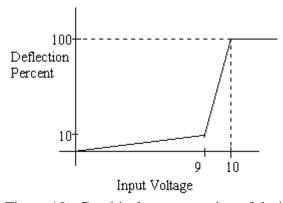

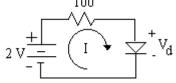

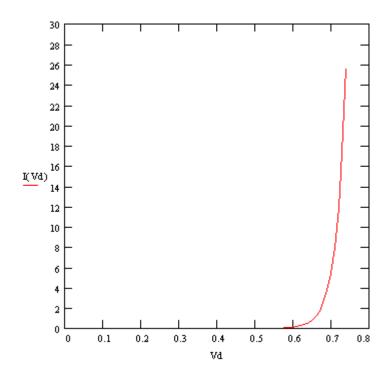

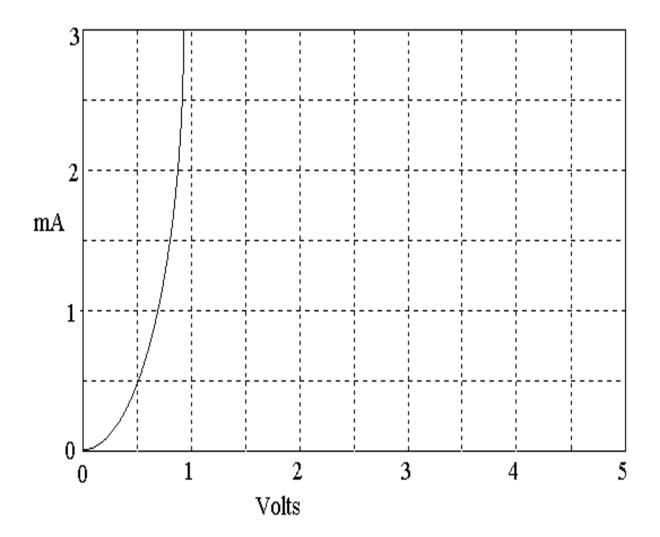

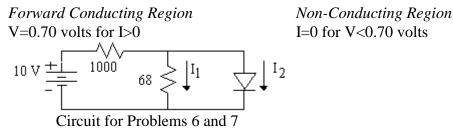

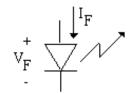

If we are going to use diodes in circuits, we must have some way to relate the voltage to the current. We will not discuss the physical electronics here, but it can be shown theoretically that the current is an exponential function of the voltage

$$I = I_s \left( e^{\left( \frac{V_d}{V_T} \right)} - 1 \right)$$

(38)

where  $I_S$  is the reverse saturation current,  $v_d$  is the voltage across the diode in the forward direction shown earlier, and  $v_T$  is the thermal voltage

$$v_T = \frac{kT}{q} \tag{39}$$

where in this case, k is Boltzman's constant, T is the temperature in  ${}^{0}K$ , and q is the electronic charge. We normally just use  $v_{T}$  in voltage form for simplicity. At room temperature,  $300 {}^{0}K$ ,  $v_{T} = 25.9 {}^{m}V$ . A plot of the diode equation is given in Figure 13. Note the change in scale for the forward and reverse currents.

Figure 13. I-V characteristic for a silicon diode.

The current flows easily when the applied voltage is equal to the built-in voltage, a point known as the flat band condition - where the conduction band energies and the valence band energies of the p region are equal to that of the n region. At this applied voltage, the depletion width is equal to zero. The capacitance is now dominated to another capacitance, known as the diffusion capacitance. This is a capacitance associated with the excess minority carriers that are injected into the p and n regions. In order to switch the diode off, these excess minority carriers must be removed from the layers in which they have been injected. Thus, there is a transient current,  $t_{rr}$ , that flow as the applied voltage on a diode is switched from  $V_a > V_{bi}$  to  $V_a < 0V$  and the minority electrons that

were injected into the p region and the minority holes that were injected into the n region return to the n region and p region, respectively.

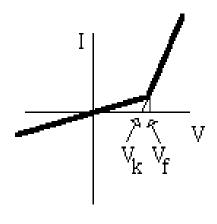

#### Non-Ideal Factors That Affect Terminal Characteristics

Because of many factors that arise during manufacturing, the measured characteristic is somewhat different. Nevertheless, for moderate current densities, the diode equation serves quite well. There are significant differences at low currents. One of the most significant is caused by surface imperfections that cause  $I_S$  to be much larger than predicted. Also,  $I_S$  is a function of temperature which can cause significant reverse leakage currents at high temperatures due to the strong temperature dependence of  $n_i$  and of the mobility of the minority carriers. At very high current densities, the resistance of the bulk semiconductor materials can have significant voltage drops that must be added to the junction characteristic to obtain the terminal characteristic. Lastly, as the reverse bias voltage is increased, at some point the p-n junction breaks down and a large amount of current flows. This reverse voltage is called the breakdown voltage,  $V_{BR}$ , and is a function of the doping levels,  $N_A$  and  $N_D$ . The closer the doping levels are to  $n_i$ , the larger  $V_{BR}$  is.

Similarly to the electron mobility in metals, the mobility of the electrons and holes in a semiconductor also have the same trend with temperature, initially increasing and then decreasing as temperature is increased. However, the relationship between resistance and temperature isn't quite as straight-forward due to the fact that the intrinsic carrier concentration, n<sub>i</sub>, has an extremely strong dependence on temperature.

To further complicate the calculation of the resistance as a function of temperature, the bandgap of the semiconductor,  $E_{\rm g}$ , is, also, a strong function of temperature. The general formula for the change in bandgap as a function of temperature is

$$E_g(T) = E_g(0K) - AT^2$$

(40)

For Si,  $E_g(0K)$  is 1.17eV, A is equal to 4.73 x  $10^{-4}$  and B is equal to 636K. T, the temperature, is in degrees Kelvin. As can be seen from the formula, the bandgap of any semiconductor decreases with increasing temperature.

This complicates the calculation of  $n_i$  as the bandgap energy is a term in the equation (see eq. 15), with the result that  $n_i$  increases even faster with increasing temperature. Because  $n_i$  increases rapidly with temperature – faster than the mobility decreases with temperature, the resistance of a semiconductor decreases with increasing temperature.

All of the thermal changes in various material properties of silicon impact the performace of a silicon p-n junction. For example, the change in the turn-on voltage  $(V_{bi})$  for silicon

# Chapter 1

diodes is approximately  $-2\text{mV}/^{\circ}\text{C}$  for changes near room temperature. Other device parameters are similarly affected by a change in temperature. The resistance of a silicon diode decreases with temperature because both the series resistance (the sum of the resistance of the bulk p-type and n-type semiconductor layers) and the junction resistance (which is inversely related to the rate of thermal generation of carriers) decrease with increasing temperature. The junction capacitance decreases with increasing temperature because the materials become less extrinsically doped as the intrinsic carrier concentration increases with temperature. When designing circuits that need to work in all types of environments – not just in the lab, engineers need to evaluate their designs to make sure that they work over the expected temperature ranges.

All of these changes limit the maximum operating temperature of silicon devices. Generally, silicon devices are limited to well under 300°C operation. Larger bandgap semiconductors are less affected by temperature and, thus, can operate to higher temperatures. SiC devices have been operated up to 600°C. Diamond diodes are expected to be able to operate at far beyond this temperature. On the other hand, HgCdTe diodes, which have an extremely small bandgap, can not operate at room temperature, but must be operated at temperatures equal to that of liquid nitrogen (77K) or below.

When you look at a data sheet, the operating temperature is specified. The manufacturer has guaranteed that the device or circuit will operate over this temperature range with the operating characteristics listed. Also, certain numerical assignments have been designated to identify the operating temperature range for some commonly used circuits. For example, digital logic circuits that begin with the numbers 74 are designed for commercial applications and generally can be operated from 0°C to 70°C. Whereas circuits that begin with the numbers 54 are designed to meet military specifications, the specified operation temperature range is –55°C to 125°C.

# **EXERCISES**

- 1. An electron is released in the middle between two metal plates which are connected to the voltage source as shown.

- a. Draw an arrow beside the electron showing which way it will move.

- b. Draw an arrow showing the direction of current.

- c. If you stood on the grounded plate and threw the electron toward the other plate, how much energy would the electron initially have to have in order to reach the other plate?

2. An intrinsic silicon material is connected to a voltage source as shown. Draw arrows indicating the directions of motion for the holes and electrons. Which direction does current flow?

Holes Electrons

Current

- 3. The doping level for an n-type silicon is  $5x10^{15}$  donors/cm<sup>3</sup>.

- a. What is the density of electrons? n =\_\_\_\_\_

- b. What is the density of holes? p = \_\_\_\_\_

- c. What is the conductivity?

$\sigma = \underline{\hspace{1cm}}$

- 4. A pn junction has a reverse saturation current  $I_o$  = 1  $\mu$ A. A forward voltage of 0.65 volts is applied. What is the current?  $I_F$  = \_\_\_\_\_\_. If a reverse voltage of 0.65 volts is applied, what is the current?  $I_R$  = \_\_\_\_\_.

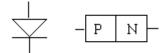

- 5. The symbol for a diode is shown along with a pn junction.

- a. Draw the polarity that will cause forward current in both devices.

- b. Draw an arrow showing the direction of forward current for both devices

#### **Problems**

- 1. Determine the conductivity of copper by using resistance and wire diameter in wire tables in the "Electrical Engineering Design Compendium".

- 2. Determine the mobility of electrons in copper which has an atomic weight of 63.54, a density of  $8.89 \times 10^3$  kg/m<sup>3</sup>, and one valence electron.

- 3. Two parallel plates 10 cm apart have a 10 volt DC voltage source connected between them. If you dropped an electron from the negative plate, how long would it take to reach the positive plate? If you stood on the positive plate and threw an electron toward the negative plate, what initial velocity is required for it to reach the negative plate?

- 4. What fraction of atoms in intrinsic silicon have broken co-valent bonds at 300°K?

- 5. You have a bar of intrinsic silicon that has a cross sectional area of 1 cm<sup>2</sup> and is 10 cm long.

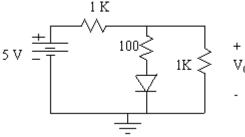

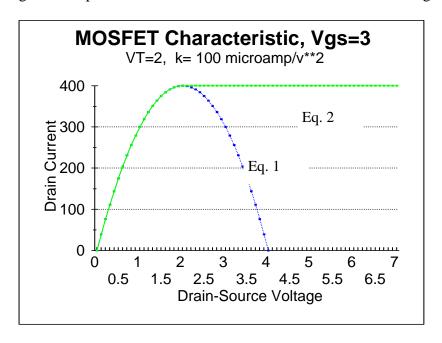

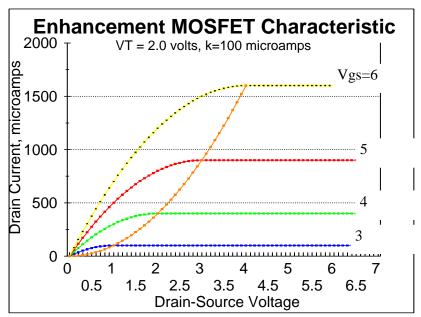

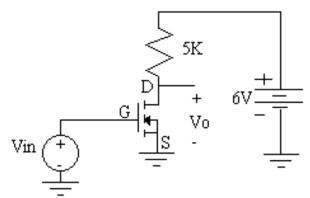

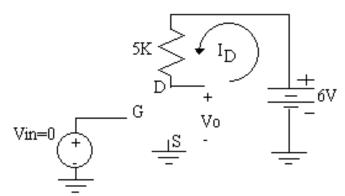

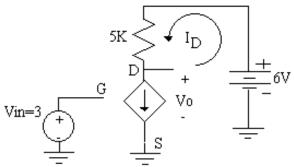

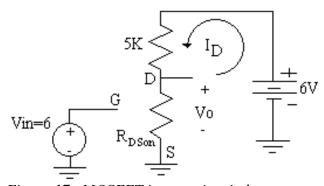

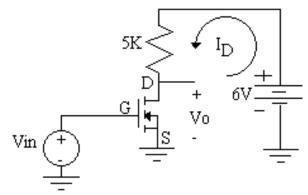

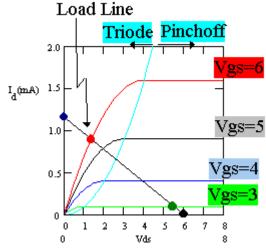

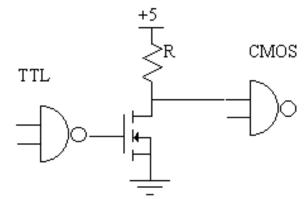

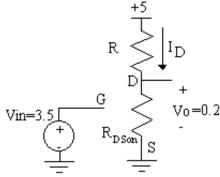

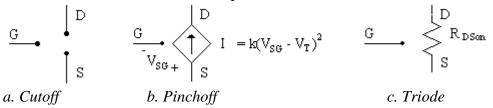

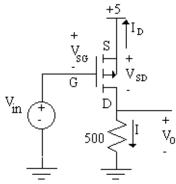

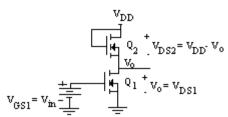

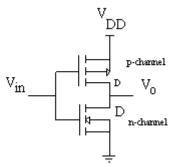

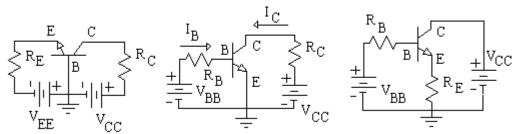

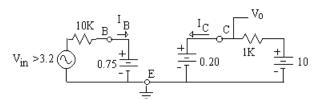

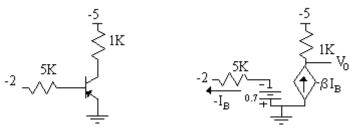

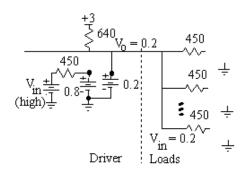

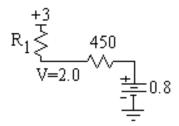

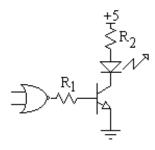

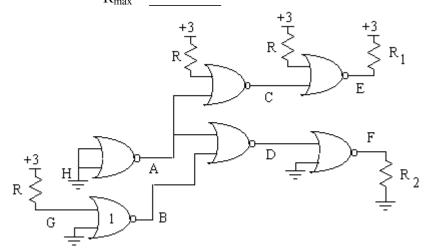

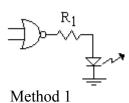

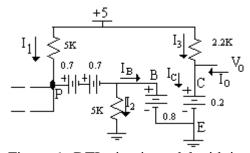

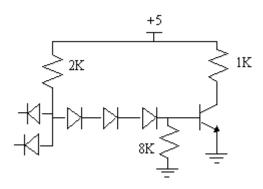

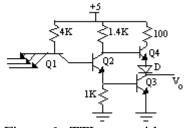

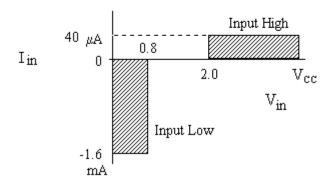

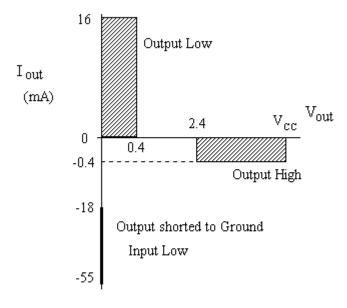

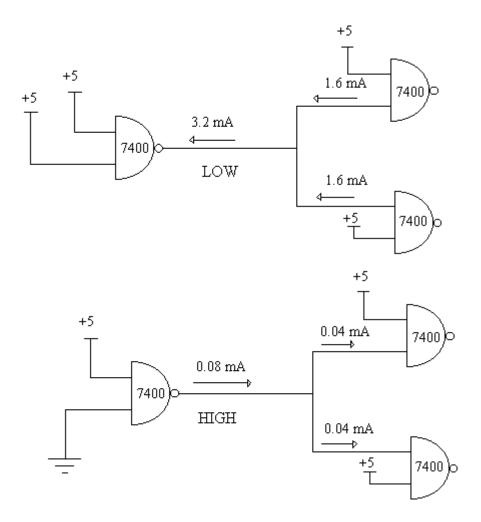

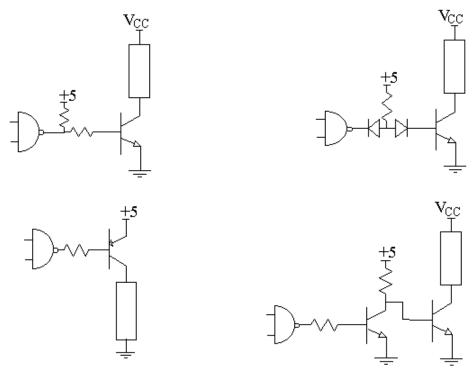

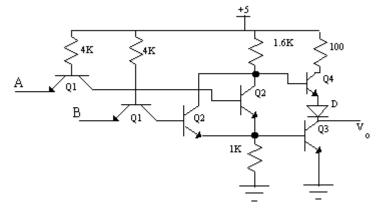

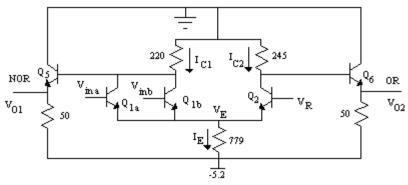

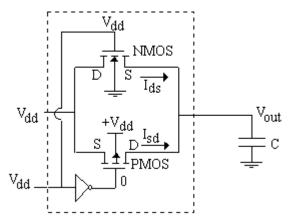

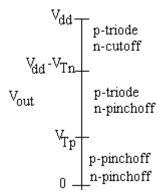

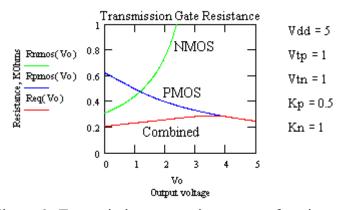

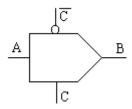

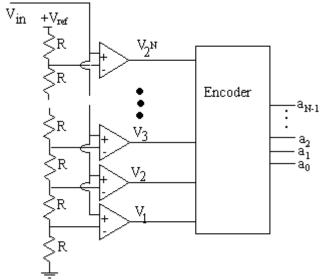

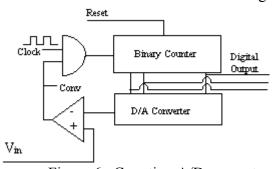

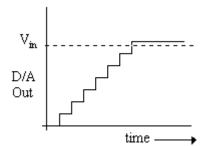

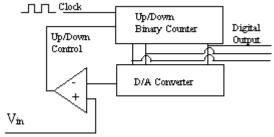

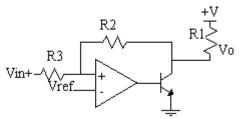

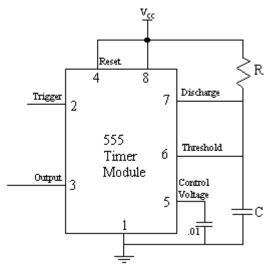

- a. What is the resistance between the ends?